# Scalable Distributed Memory Multiprocessors

Todd C. Mowry CS 418 March 22 & 23, 2011

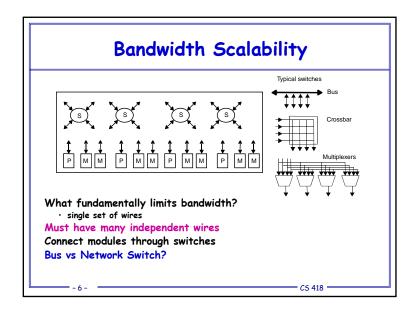

# Limited Scaling of a Bus

Characteristic Bus ~ 1 ft Physical Length **Number of Connections** Maximum Bandwidth fixed Interface to Comm. medium memory interface Global Order arbitration Protection virtual memory Trust os HW comm. abstraction

Bus: each level of the system design is grounded in the scaling limits at the layers below and assumptions of close coupling between components

3 - \_\_\_\_\_\_ CS 418

# Outline

## Scalability

- · physical, bandwidth, latency and cost

- · level of integration

# Realizing Programming Models

- · network transactions

- · protocols

- · safety

- input buffer problem

- fetch deadlock

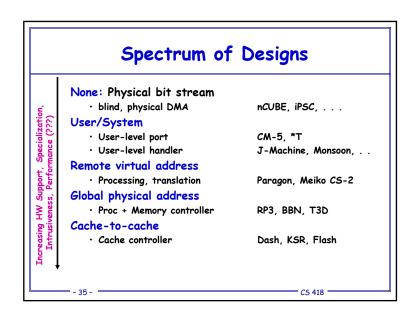

# Communication Architecture Design Space

· how much hardware interpretation of the network transaction?

-2- CS 418

# PCs in a LAN?

LAN Characteristic KM Physical Length ~ 1 ft Number of Connections fixed many Maximum Bandwidth fixed ??? Interface to Comm. medium memory interface peripheral Global Order arbitration Protection virtual memory os Trust total none single independent comm. abstraction

No clear limit to physical scaling, little trust, no global order, consensus difficult to achieve.

Independent failure and restart

- 4 - CS 418

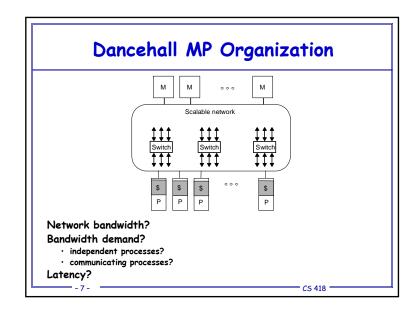

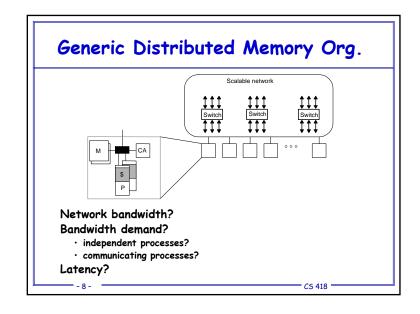

# Scalable Machines What are the design trade-offs for the spectrum of machines between?

- · specialize or commodity nodes?

- · capability of node-to-network interface

- · supporting programming models?

## What does scalability mean?

- · avoids inherent design limits on resources

- · bandwidth increases with P

- · latency does not

- · cost increases slowly with P

CS 418

# **Key Property**

Large # of independent communication paths between nodes

· allow a large # of concurrent transactions using different wires

Initiated independently

No global arbitration

Effect of a transaction only visible to the nodes involved

· effects propagated through additional transactions

- 9 - CS 418

# Typical Example

max distance: log P

number of switches:  $\alpha P \log P$

overhead = 1 us, BW = 64 MB/s, 200 ns per hop

### Store and Forward

$T_{64}^{s}(128) = 1.0 \text{ us} + 6 \text{ hops} * (2.0 + 0.2) \text{ us/hop} = 14.2 \text{ us}$  $T_{61024}^{s}(128) = 1.0 \text{ us} + 10 \text{ hops} * (2.0 + 0.2) \text{ us/hop} = 23 \text{ us}$

### **Pipelined**

$T_{64}(128)$  = 1.0 us + 2.0 us + 6 hops \* 0.2 us/hop = 4.2 us  $T_{1024}(128)$  = 1.0 us + 2.0 us + 10 hops \* 0.2 us/hop = 5.0 us

- 11 - C5 418

# Latency Scaling

T(n) = Overhead + Channel Time + Routing Delay

Overhead?

Channel Time(N) = N/B

· N = # of bytes in message

• B = bandwidth of channel's bottleneck

Routing Delay(H,N)

· H = # of hops to route message

- 10 - CS 418

# Cost Scaling

cost(P,M) = fixed cost + incremental cost (P,M)

· P = # of processors, M = amount of memory

Bus Based SMP?

Ratio of processors : memory : network : I/O ?

Parallel efficiency(p) = Speedup(P) / P

Costup(p) = Cost(P) / Cost(1)

Cost-effective: Speedup(P) > Costup(P)

- 12 - \_\_\_\_\_\_ C5 418

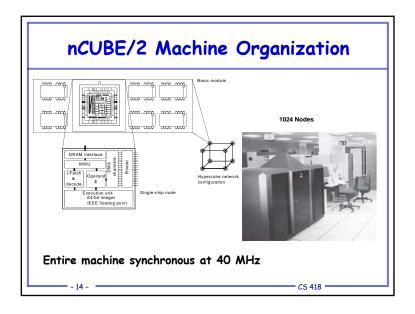

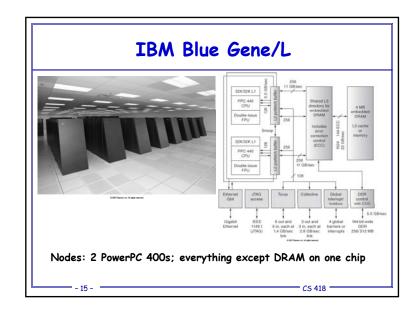

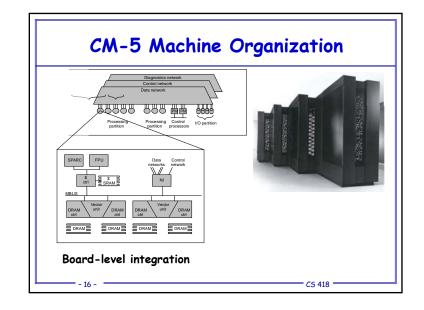

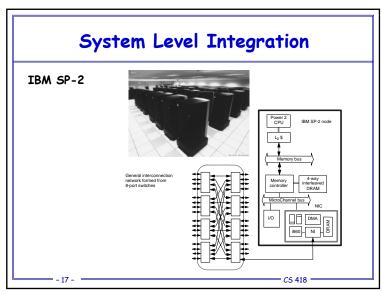

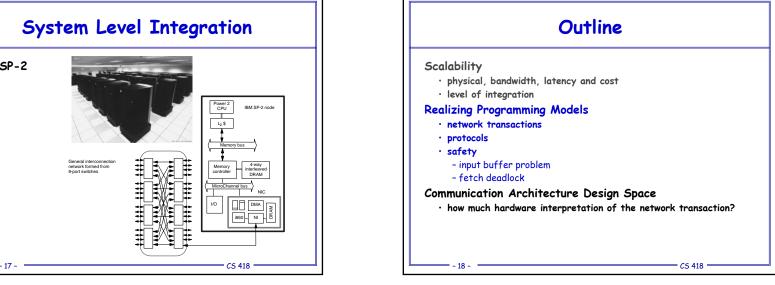

# Physical Scaling

# Different Levels of Integration:

- · Chip-level integration

- · Board-level integration

- · System-level integration

- 13 - CS 418 =

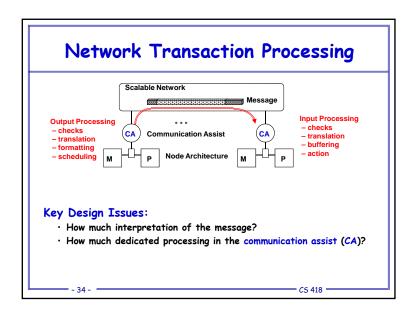

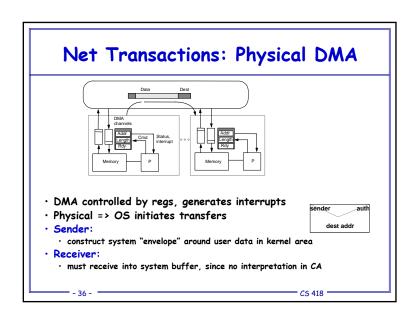

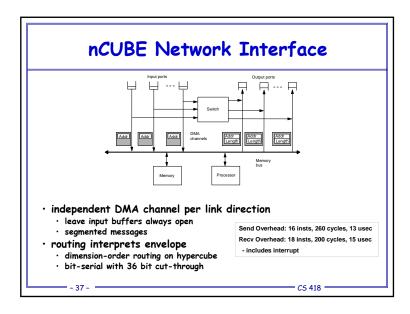

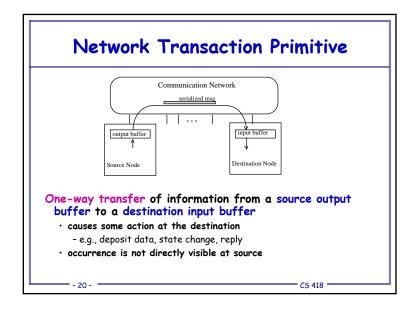

# Bus Transactions vs. Network Transactions

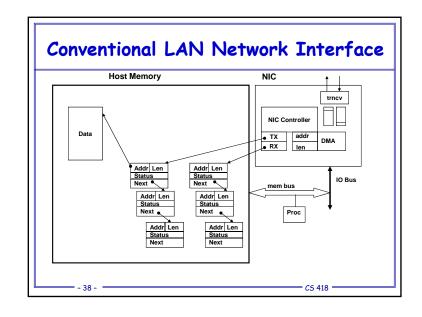

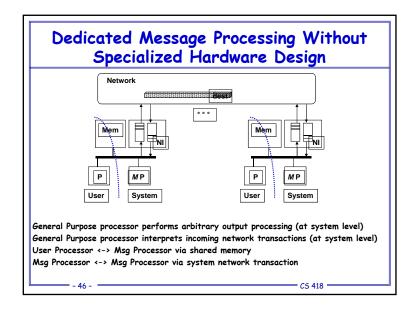

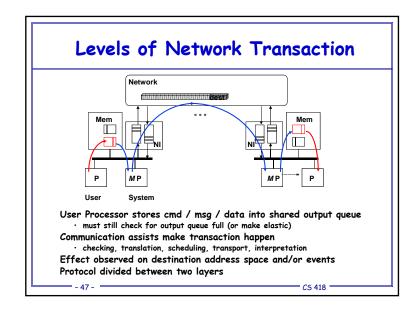

Issues: Bus Network V->P 22 protection check format flexible wires output buffering reg, FIFO 23 media arbitration global local destination naming and routing input buffering limited many source action completion detection

- 21 - C5 418

# The Fetch Deadlock Problem

- Even if a node cannot issue a request, it must sink network transactions.

- Incoming transaction may be a request, which will generate a response.

- · Closed system (finite buffering)

- 23 - CS 418 =

# Shared Address Space Abstraction

## Fundamentally a two-way request/response protocol

· writes have an acknowledgement

### Issues:

- · fixed or variable length (bulk) transfers

- · remote virtual or physical address, where is action performed?

- · deadlock avoidance and input buffer full

- · cache coherence and memory consistency (discussed earlier)

- - 22 - \_\_\_\_\_\_ CS 410

# Key Properties of SAS Abstraction

- Source and destination data addresses are specified by the source of the request

- · a degree of logical coupling and trust

- No storage logically "outside the application address space(s)"

- may employ temporary buffers for transport

- Operations are fundamentally request-response

- · Remote operation can be performed on remote memory

- · logically does not require intervention of the remote processor

24 - \_\_\_\_\_\_ CS 418

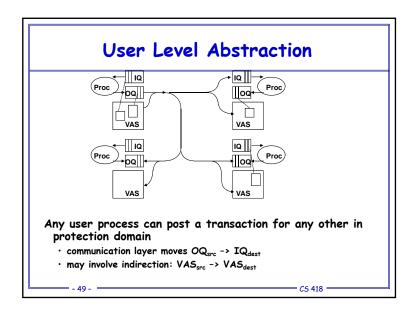

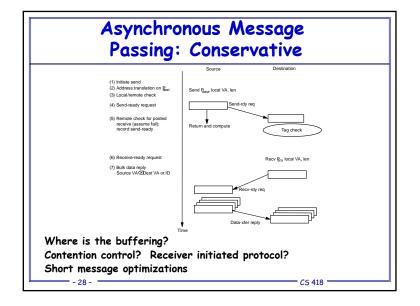

# Message Passing

### **Bulk transfers**

### Complex synchronization semantics

- · more complex protocols

- · more complex action

### **Synchronous**

- · Send completes after matching recv and source data sent

- Receive completes after data transfer complete from matching send

### Asynchronous

· Send completes after send buffer may be reused

- 25 - CS 418

# Synchronous Message Passing Source Destination Recv & local VA, len (1) Initiate send (2) Address translation on Bc. (3) Local/renote check (4) Send-ready request (6) Remote check for posted receive (assume success) (6) Reply transaction (7) Bulk data transfer Source VA-CDest VA or ID Constrained programming model. Deterministic! What happens when threads added? Destination contention very limited. User/System boundary? -26-

# Asynch. Message Passing: Optimistic Source Destination (1) Initiate send (2) Address translation Send (Rest, local VA, len) (3) Local/remote check (4) Send data (5) Remote check for posted receive: on fail. Tag match Allocate buffer Recv Pro local VA, len More powerful programming model Wildcard receive => non-deterministic Storage required within message layer? CS 418

# Key Features of Message Passing Abstraction

# Source knows send data address, destination knows receive data address

· after handshake they both know both

## Arbitrary storage "outside the local address spaces"

- · may post many sends before any receives

- non-blocking asynchronous sends reduces the requirement to an arbitrary number of descriptors

- fine print says these are limited too

## Fundamentally a 3-phase transaction

- · includes a request / response

- · can use optimistic 1-phase in limited "safe" cases

- credit scheme

- 29 - CS 418

# Common Challenges (Cont)

### Avoiding Fetch Deadlock

- For network to remain deadlock free, nodes must continue accepting messages, even when cannot source msgs

- · what if incoming transaction is a request?

- each may generate a response, which cannot be sent!

- what happens when internal buffering is full?

### Approaches:

- 1. Logically independent request/reply networks

- physical networks

- virtual channels with separate input/output queues

- 2. Bound requests and reserve input buffer space

- K(P-1) requests + K responses per node

- service discipline to avoid fetch deadlock?

- 3. NACK on input buffer full

- NACK delivery?

- 31 - CS 418

# Common Challenges

### Avoiding Input Buffer Overflow

· requires flow-control on the sources

### Approaches:

- 1. Reserve space per source (credit)

- when available for reuse?

- » explicit ack or higher-level feedback

- 2. Refuse input when full

- backpressure in reliable network

- tree saturation

- deadlock free

- what happens to traffic not bound for congested destination?

- 3. Reserve ack back channel

- 4. Drop packets

- 5. Utilize higher-level semantics of programming model

- 30 - CS 418

# Challenges in Realizing Programming Models in the Large

- · One-way transfer of information

- No global knowledge, nor global control

- · barriers, scans, reduce, global-OR give fuzzy global state

- · Very large number of concurrent transactions

- · Management of input buffer resources

- many sources can issue a request and over-commit destination before any see the effect

- Latency is large enough that you are tempted to "take risks"

- · optimistic protocols

- · large transfers

- · dynamic allocation

- Many many more degrees of freedom in design and engineering of these system

- 32 - \_\_\_\_\_\_\_ CS 418

# Scalability • physical, bandwidth, latency and cost • level of integration Realizing Programming Models • network transactions • protocols • safety • input buffer problem • fetch deadlock Communication Architecture Design Space • how much hardware interpretation of the network transaction?