#### CHIP MULTIPROCESSORS FOR SERVER WORKLOADS

NIKOLAOS HARDAVELLAS

CMU-CS-09-150

JULY 2009

SCHOOL OF COMPUTER SCIENCE COMPUTER SCIENCE DEPARTMENT CARNEGIE MELLON UNIVERSITY

#### **Thesis Committee:**

Babak Falsafi, co-Chair Anastasia Ailamaki, co-Chair David R. O'Hallaron Todd C. Mowry Luiz André Barroso (Google)

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

© Copyright 2009 by Nikolaos Hardavellas All Rights Reserved

This research was sponsored by equipment donations from Intel, two Sloan research fellowships, an ESF European Young Investigator award, an IBM faculty partnership award, and the National Science Foundation under grants CCR-0205544, CCF-0702658, CCR-0509356, CCF-0845157, IIS-0133686, and IIS-0713409. The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of any sponsoring institution, the U.S. government or any other entity.

**Keywords:** computer architecture, cache, multicore, chip multiprocessors, data placement, chip design, NUCA, commercial server workloads, performance modeling, design-space exploration.

to our family

to Jasmine

to Kivanc where you are, is paradise

## Abstract

We stand on the cusp of the giga-scale era of chip integration. Technological advancements in semiconductor fabrication yield ever-smaller and faster devices, enabling billion-transistor chips with multi-gigahertz clock frequencies. To utilize the abundant transistors on chip, modern processors pack an exponentially increasing number of cores on chip, multi-megabyte caches, and large interconnects to facilitate intra-chip data transfers. However, the growing on-chip resources do not directly translate into a commensurate increase in performance. Rather, they come at the cost of increased on-chip data access latency, while thermal considerations and pin constraints limit the parallelism that a multicore chip can support.

To mitigate the increasing on-chip data access latency, cache blocks on chip should be placed close to the cores that use them. We observe that cache access patterns can be classified at run time into distinct classes with different on-chip block placement requirements. Based on this observation, we propose Reactive NUCA (R-NUCA), a distributed cache design which reacts to the class of each access to place blocks close to the requesting cores. We then explore the design space of physically-constrained multicore processors, and find that future multicores should utilize low-operational-power transistors even for time-critical components (e.g., cores) to ease the power wall, employ novel on-chip block placement techniques to utilize efficiently large caches, while techniques like 3D-stacked memory can mitigate the off-chip bandwidth constraint even for peakperformance designs. Moving forward, we find that heterogeneous multicores hold great promise in improving designs even further.

## Acknowledgements

Any success I have had, I owe to my advisors, Babak Falsafi and Anastasia Ailamaki. They taught me how to think and do research, how to speak and write. Their penetrating insights have been a source of inspiration for this work. But, foremost, they have been my dear friends; always eager to help, always there when I need them the most. Thank you!

I am grateful to my thesis committee, Dave O'Hallaron, Todd Mowry, and Luiz André Barroso. Their support has been unwavering, and their comments and suggestions have improved this work tremendously. I thank you all for your collaboration and gracious help, and for making the thesis process such a pleasurable experience. I also owe special thanks to Andreas Moshovos for generously devoting a lot of his time to me.

I wouldn't have gone into research, if it wasn't for Marios Mavronicolas, an amazing teacher and great friend who took me under his wings early in my student life and offered me my first research experience. Thankfully for the field of theoretical computer science, but sadly for computer architecture, later I decided to switch research areas.

There are a lot of people who supported me at Carnegie Mellon, and without their help this work would never be possible. They have all been my mentors and my dear friends. Brian Gold tolerated me as an office-mate, and provided invaluable input and support, both for my work as well as outside the office. Stephen Somogyi and Mike Ferdman put countless hours towards helping me decipher results and polish papers and talks. Tom Wenisch made our research infrastructure possible. Jared Smolens often put his incredible skills to the help of others. Eric Chung was always ready for long and deep research discussions. Thank you all for everything.

If it was not for my wife, Kivanc Sabirli, I would have truly lost my mind at various stages of my thesis work. Her unconditional support kept me going; her infinite love put a purpose in my life and reminded me of what truly matters; her smile gave me power to hike the thesis mountain. Kivanc, I couldn't have done it without you. You are my home. Long time [sic].

I've watched countless dawns with Jasmine and Lilly after a night of hard work, listening to birds upon the first break of the morning light. They kept me company in the wee hours, Jasmine sitting on my chair or on the warm laptop, Lilly laying on the keyboard when it was time for a break. Jasmine and Lilly, thank you for your warm company. You'll always be with us.

This section would never be complete without expressing my sincere gratitude to our family. The unconditional love and support of Yiannis, Yiota, and Themis pulled me through rough seas and taught me the value of education. This dissertation is as much their accomplishment, as it is mine. The enormous hospitality and love of Hikmet, Semra, Isik and Erhan warmed my heart when I needed it the most. I can only aspire sometime to be as gentle and thoughtful as they are.

I am grateful to Leonidas Kontothanassis and Cindy Arens. Their friendship and encouragement has been instrumental throughout my life. They are among the most generous people I have ever met, and I owe them more than I can ever put in words. Special thanks are also due to Alexandros Labrinidis. His hospitality allowed me to proceed undeterred in the last stages of the thesis, and his friendship, mentoring and support have helped me tremendously throughout my career.

Sotiris Damouras has been the ideal house-mate. His friendship and support has filled our life in Pittsburgh with warm memories, and our breaks at the porch provided a much-needed

respite. Vagelis Vlachos and Michael Papamichael helped me put work aside once in a while and enjoy life, and supported me a lot at the last stages of this effort. Takis, Maria, Tina, Panos, Areti, Kostas, Ioanna, Manos, Liz, Eleni, Tania, Yiannis, Pantelis and Ippokratis have always opened their houses to us and hosted parties and cook-outs that cleared my head and recharged my mind. Thank you all for helping me keep my sanity.

I wish to thank the roasters at Vivace for their amazing coffee, the people at Isomac for their great coffee machines, and at Mazzer for their grinders. Matt Koeske for introducing me to the culture of espresso aficionados and fine teas. The A-level faculty for making sure my cup was always full. The Brothers K Coffee House in Evanston, IL for providing me with an office during the last month of the thesis writing, and for making sure my cup remained bottomless. James Hoe for the Friday lunch series that kept us all connected, and for his advise and support whenever requested.

There are a lot more people to thank, and a hundred pages would not suffice to list them all. Please, permit me to thank you all at once and take this acknowledgement as an invitation to toast yourselves, wherever you might be.

I sincerely hope you enjoy reading.

х

# Table of Contents

| Abstract     |                                                      | v    |

|--------------|------------------------------------------------------|------|

| Acknowled    | gements                                              | vii  |

| List of Figu | ıres                                                 | XV   |

| List of Tab  | les                                                  | xvii |

| Chapter 1    | Introduction                                         | 1    |

| 1.1          | Performance Analysis of Modern CMPs                  | 2    |

| 1.2          | Near-Optimal On-Chip Block Placement and Replication | 4    |

| 1.3          | Optimal CMPs Across Technologies                     | 6    |

| 1.4          | Contributions                                        | 7    |

| Chapter 2    | Performance Analysis of CMPs                         | 11   |

| 2.1          | Introduction                                         |      |

| 2.2          | CMP Camps and Workloads                              | 14   |

|              | 2.2.1 Fat Camp vs. Lean Camp                         |      |

|              | 2.2.2 Unsaturated vs. Saturated Workloads            |      |

| 2.3          | Experimental Methodology                             |      |

| 2.4          | DBMS Performance on CMPs                             | 21   |

| 2.5          | Analysis of Data Stalls                              |      |

|              | 2.5.1 Impact of On-Chip Cache Size                   |      |

|              | 2.5.2 Impact of Core Integration on Single Chip      |      |

|              | 2.5.3 Impact of On-Chip Core Count                   |      |

|              | 2.5.4 Ramifications                                  |      |

xi

| 2.6       | Summary                                            |    |

|-----------|----------------------------------------------------|----|

| Chapter 3 | Reactive NUCA                                      |    |

| 3.1       | Background                                         |    |

|           | 3.1.1 Non-Uniform Cache Architectures              |    |

|           | 3.1.2 Tiled Architectures                          |    |

|           | 3.1.3 Requirements for Intelligent Block Placement | 41 |

| 3.2       | Characterization of L2 References                  |    |

|           | 3.2.1 Methodology                                  | 41 |

|           | 3.2.2 Categorization of Cache Accesses             |    |

|           | 3.2.3 Characterization of Access Classes           |    |

|           | 3.2.4 Characterization Conclusions                 |    |

| 3.3       | R-NUCA Design                                      |    |

|           | 3.3.1 Indexing and Rotational Interleaving         | 54 |

|           | 3.3.2 Placement                                    |    |

|           | 3.3.3 Page Classification                          |    |

|           | 3.3.4 Extensions                                   | 60 |

|           | 3.3.5 Generalized Form of Rotational Interleaving  | 61 |

| 3.4       | Evaluation                                         |    |

|           | 3.4.1 Methodology                                  |    |

|           | 3.4.2 Classification Accuracy                      |    |

|           | 3.4.3 Impact of R-NUCA Mechanisms                  |    |

|           | 3.4.4 Performance Improvement                      | 74 |

|           | 3.4.5 Impact of Technology                         |    |

| 3.5       | Summary                                            |    |

| Chapter 4 | Optimal CMPs Across Technologies                   |    |

| 4.1       | First-Order Analytical Modeling                    |    |

|           | 4.1.1 Technology Model                             |    |

|           | 4.1.2 Hardware Model                               |    |

|           | 4.1.3 Area Modeling of Hardware Components         |    |

|           | 4.1.4 Performance Modeling                         |    |

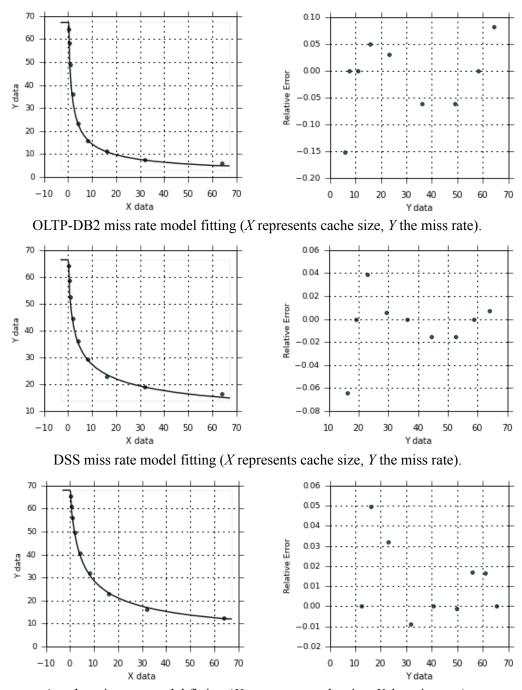

|             | 4.1.5 Miss Rate Model and Application Dataset Evolution |     |

|-------------|---------------------------------------------------------|-----|

|             | 4.1.6 Power Models                                      |     |

|             | 4.1.7 Off-Chip Bandwidth Model                          |     |

|             | 4.1.8 Modeling 3D-Stacked Memory                        |     |

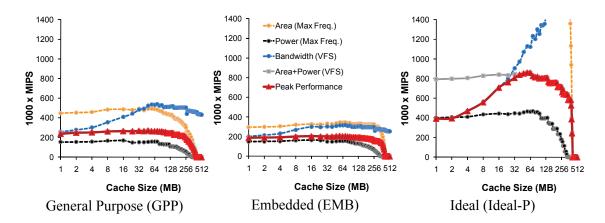

| 4.2         | Peak-Performing Designs Under Physical Constraints      | 95  |

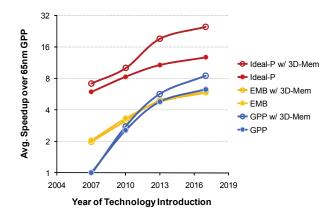

| 4.3         | Physically-Constrained Designs Across Technologies      | 99  |

|             | 4.3.1 Multicore Processors With milliWatt Cores         | 101 |

|             | 4.3.2 CMPs with Ideal Cores                             |     |

|             | 4.3.3 CMPs with 3D-Stacked Memory                       | 106 |

| 4.4         | Summary                                                 |     |

| Chapter 5   | Related Work                                            |     |

| Chapter 6   | Future Work                                             | 117 |

| Chapter 7   | Conclusions                                             | 121 |

| Bibliograph | ıy                                                      | 123 |

.

xiii

xiv

# List of Figures

| Figure     | Title                                                              | Page |

|------------|--------------------------------------------------------------------|------|

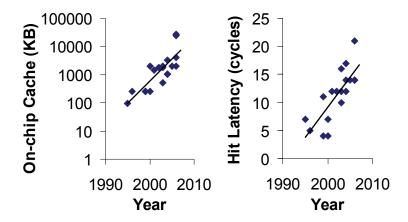

| FIGURE 1:  | Historic trends of on-chip caches on (a) size, and (b) latency     | 3    |

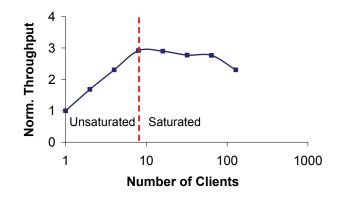

| FIGURE 2:  | Unsaturated vs. saturated workloads.                               | 17   |

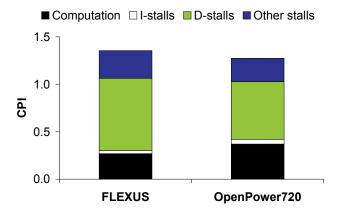

| FIGURE 3:  | validation using the saturated DSS workload                        | 20   |

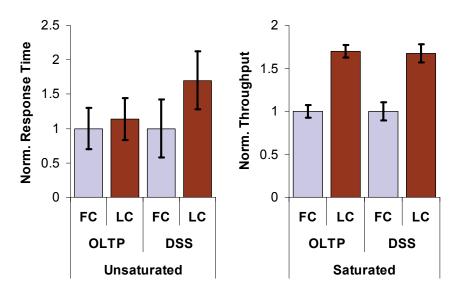

| FIGURE 4:  | (a) Response time and (b) throughput of LC normalized to FC        | 22   |

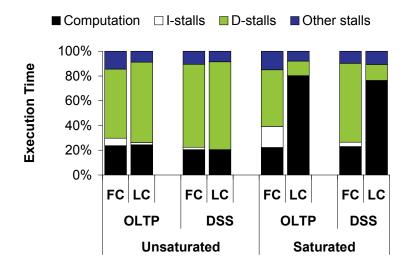

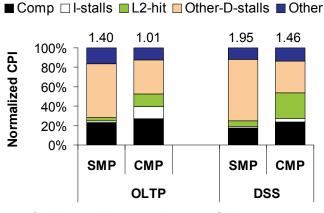

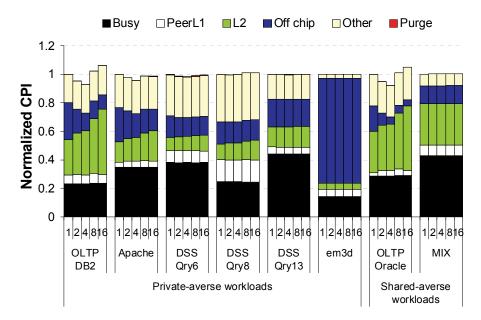

| FIGURE 5:  | Breakdown of execution time                                        | 23   |

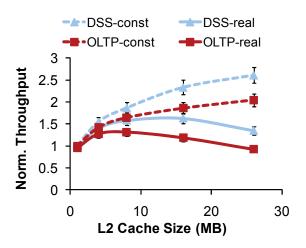

| FIGURE 6:  | Effect of cache size and latency on throughput                     | 25   |

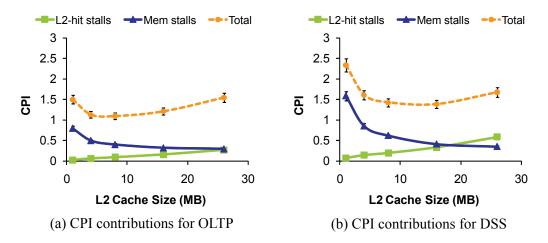

| FIGURE 7:  | Effect of cache size and latency on CPI for (a) OLTP and (b) DSS   |      |

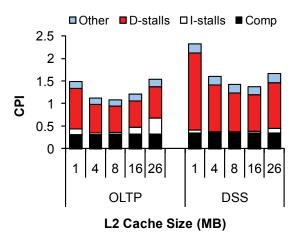

| FIGURE 8:  | CPI breakdown with increasing L2 size.                             | 27   |

| FIGURE 9:  | Impact of chip multiprocessing on CPI.                             |      |

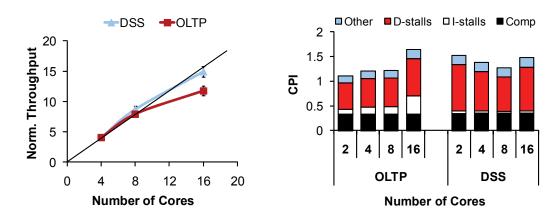

| FIGURE 10: | Impact of core count on (a) throughput, and (b) CPI breakdown      | 29   |

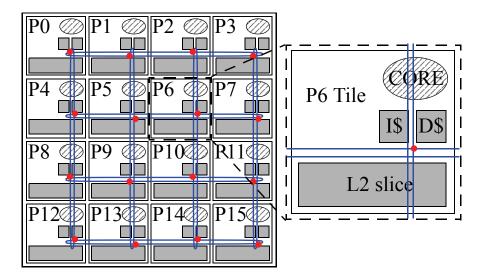

| FIGURE 11: | Typical tiled architecture and floorplan of folded 2D-torus        |      |

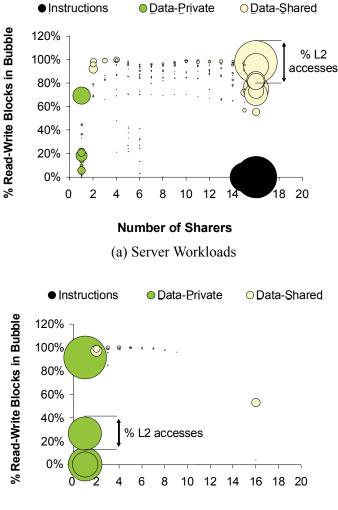

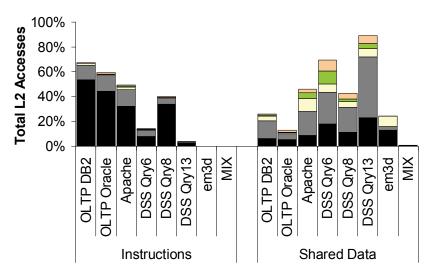

| FIGURE 12: | L2 Access Categorization and Clustering.                           | 44   |

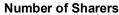

| FIGURE 13: | L2 Reference breakdown                                             | 45   |

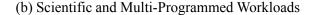

| FIGURE 14: | L2 working set sizes for private data, instruction and shared data | 47   |

| FIGURE 15: | Instruction and shared data reuse by same core.                    | 49   |

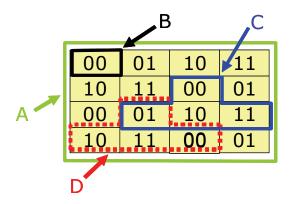

| FIGURE 16: | Example of R-NUCA clusters and Rotational Interleaving.            | 53   |

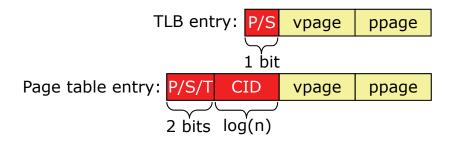

| FIGURE 17: | Page table entry and TLB extensions.                               | 56   |

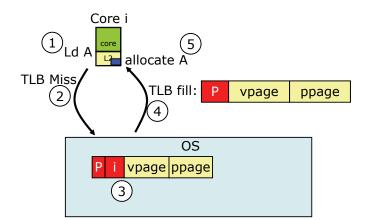

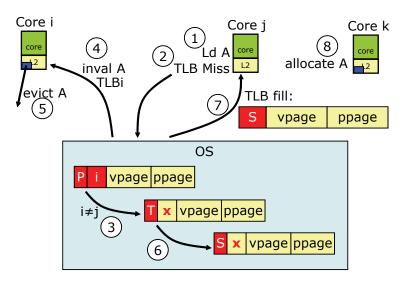

| FIGURE 18: | Time-line of private page classification.                          | 57   |

| FIGURE 19: | Time-line of shared-data page classification.                      | 58   |

| FIGURE 20: | RIDs and examples for size-8 and size-16 fixed-center clusters     | 63   |

.

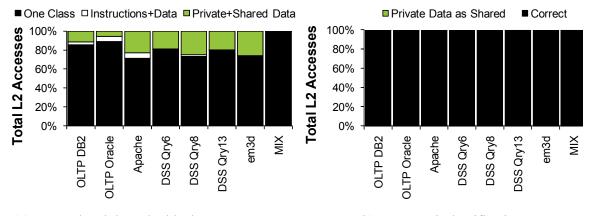

| FIGURE 21: | Page-grain access types and misclassifications.                  | 66  |

|------------|------------------------------------------------------------------|-----|

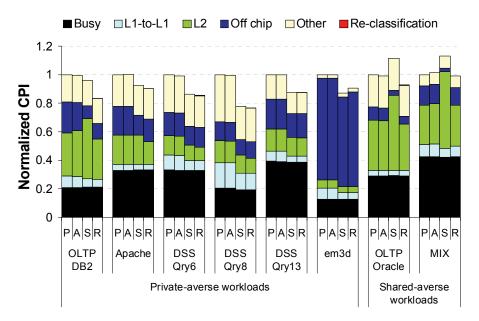

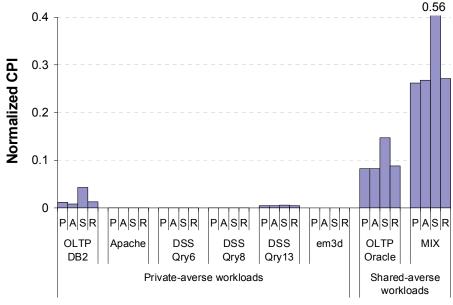

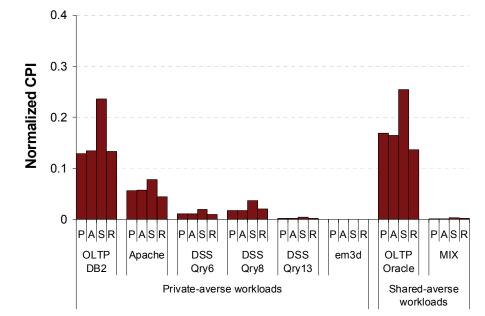

| FIGURE 22: | Total CPI breakdown for L2 designs.                              | 67  |

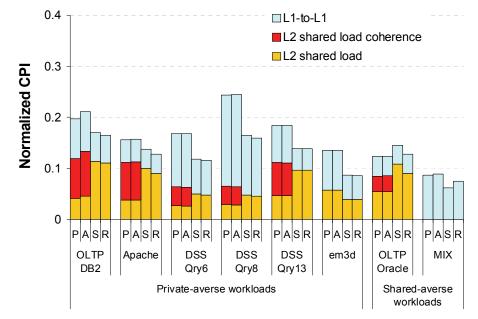

| FIGURE 23: | CPI breakdown of L1-to-L1 and L2 load accesses.                  | 69  |

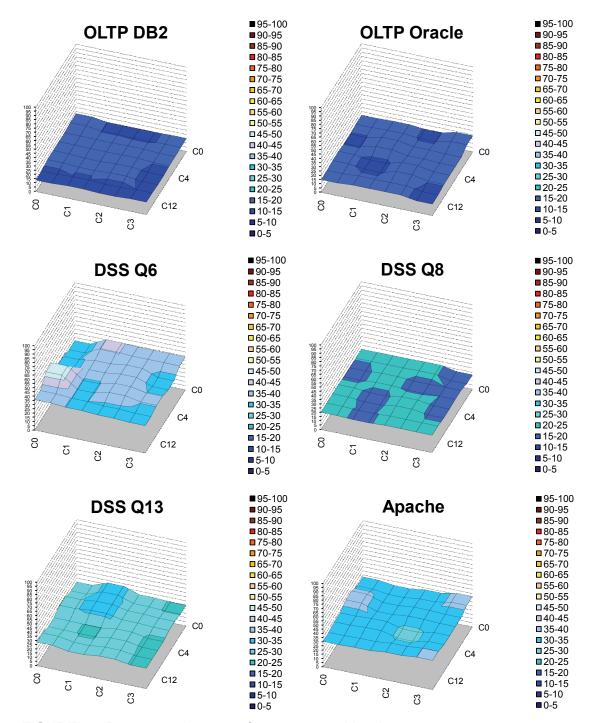

| FIGURE 24: | CPI contribution of L2 accesses to private data                  | 70  |

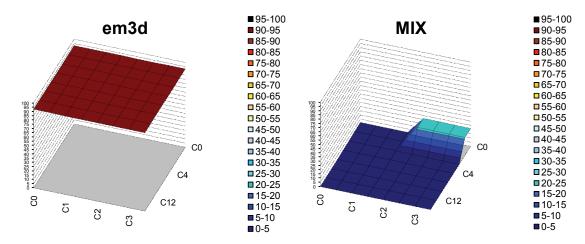

| FIGURE 25: | Per-core miss rates for scientific and multiprogrammed workloads | 71  |

| FIGURE 26: | Per-core miss rates for server workloads.                        | 72  |

| FIGURE 27: | CPI contribution of L2 instruction accesses.                     | 73  |

| FIGURE 28: | CPI breakdown of instruction clusters with various sizes.        | 74  |

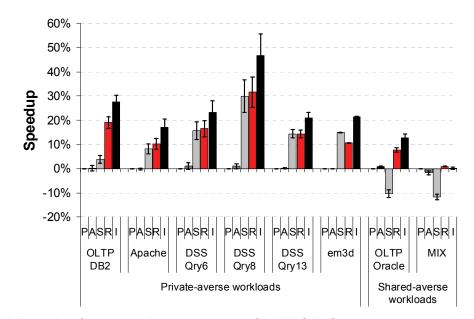

| FIGURE 29: | Performance Improvement of R-NUCA.                               | 75  |

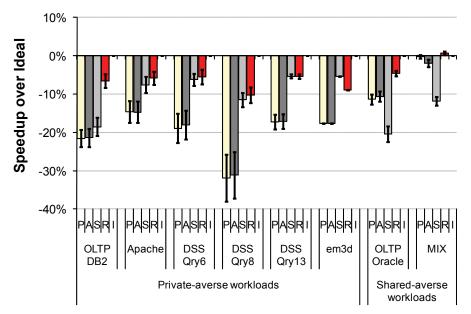

| FIGURE 30: | Performance of R-NUCA relative to Ideal.                         | 76  |

| FIGURE 31: | Miss rate model fitting (left) and relative error plots (right). | 88  |

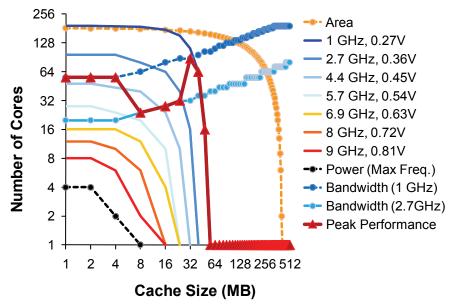

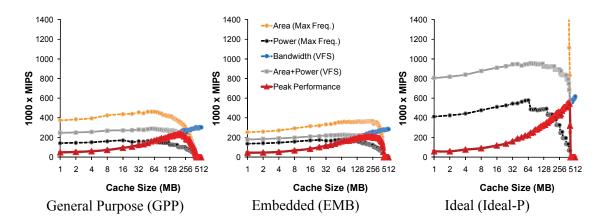

| FIGURE 32: | Core count-cache size trade-off subject to physical constraints. | 96  |

| FIGURE 33: | Performance of physically-constrained designs                    | 98  |

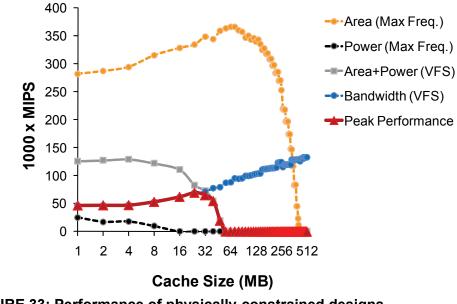

| FIGURE 34: | Performance of GPP CMPs across technologies and device types     | 100 |

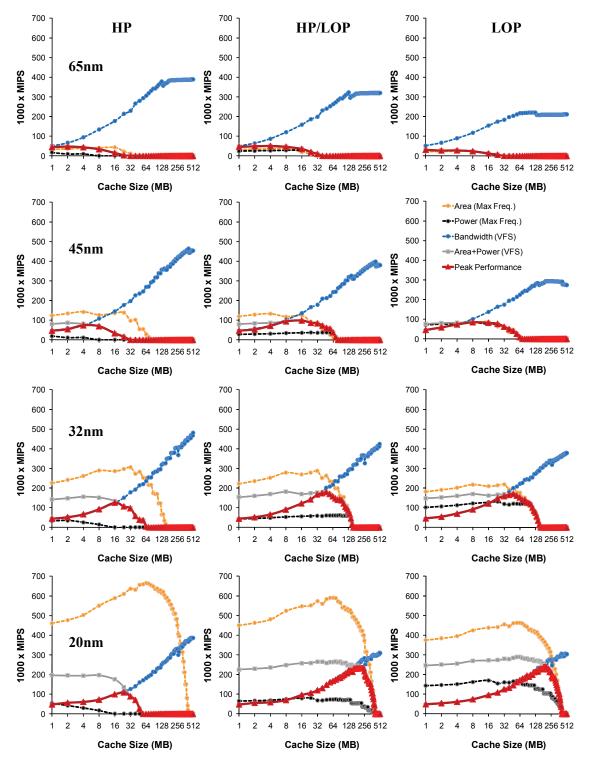

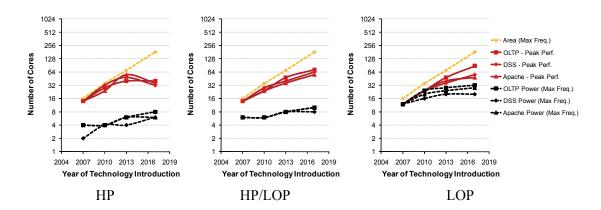

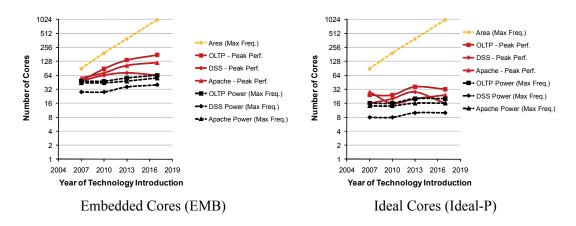

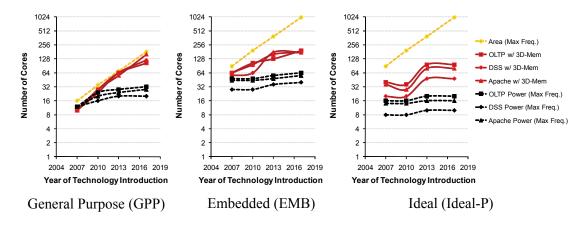

| FIGURE 35: | Core count for peak-performance HP, HP/LOP and LOP designs       | 101 |

| FIGURE 36: | Performance of GPP, EMB, and Ideal-P 20nm CMPs running OLTP      | 102 |

| FIGURE 37: | Core count of CMPs with embedded and ideal cores.                | 103 |

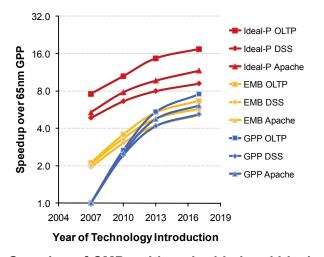

| FIGURE 38: | Speedup of CMPs with embedded and ideal cores.                   | 104 |

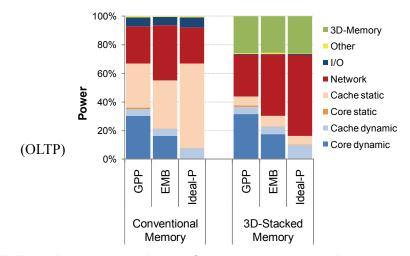

| FIGURE 39: | Power breakdown of conventional and 3D-memory CMPs at 20nm       | 105 |

| FIGURE 40: | GPP, EMB and Ideal-P CMPs at 20nm with 3D-memory (OLTP)          | 106 |

| FIGURE 41: | Speedup of CMPs with conventional and 3D-stacked memory          | 107 |

| FIGURE 42: | Core counts for CMPs with 3D-stacked memory.                     | 108 |

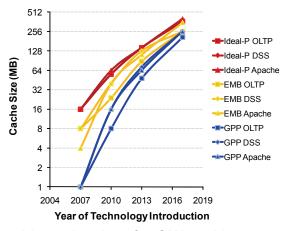

| FIGURE 43: | On-chip cache sizes for CMPs with conventional memory            | 109 |

# List of Tables

| Table    | Title                                             | Page |

|----------|---------------------------------------------------|------|

| Table 1: | Chip multiprocessor camp characteristics          | 15   |

| Table 2: | System parameters for the 8-core and 16-core CMPs | 42   |

| Table 3: | Workload parameters for R-NUCA evaluation.        | 43   |

| Table 4: | Performance Model Parameters.                     | 83   |

| Table 5: | Miss Rate Model Parameters                        | 87   |

.

xvii

xviii

# Chapter 1

## Introduction

Commercial server software systems (e.g., database management systems, web servers) are at the center of a multi-billion dollar server industry, utilizing state-of-the-art processors to maximize performance. Over the past decades, processor designs focused primarily on improving performance by exploiting instruction-level parallelism (ILP). The resulting wide-issue out-of-order (OoO) processors overlap both computation and memory accesses to increase performance, but fall short of realizing their full potential when running server workloads. Many important server workloads exhibit large instruction footprints and tight data dependencies that reduce instructionlevel parallelism and incur data and instruction transfer delays [2,79,93,101].

Thus, increasingly aggressive OoO techniques yield diminishing returns in performance, while their power dissipation is reaching prohibitive levels [14]. The shortcomings of out-of-order processors, along with the continued increase in the number of transistors available on chip, have encouraged most vendors to integrate multiple processors on a single chip, instead of simply increasing the complexity of individual cores. Major manufacturers already ship 8-core chip multiprocessors [61] with plans to scale to 100s of cores [8,86]. Specialized vendors already push the envelope further, with Cisco CRS-1 featuring 188 processing cores, Tilera's TILE64 with 64 cores, and Azul Vega 3 with 54 out-of-order cores.

The resulting chip multiprocessor (CMP) designs may increase processor stalls through promoting on-chip data sharing across cores and increasing contention for shared hardware resources. However, to date, there hasn't been a comprehensive study that examines how the emerging hardware trends affect the performance of server workloads.

#### 1.1 Performance Analysis of Modern CMPs

Recent studies show that processors are far from realizing their maximum performance when executing commercial server workloads. Prior research [75, 101] indicates that the adverse memory access patterns in commercial server workloads result in poor cache locality and overall performance. Server workloads are known to spend at least half of their execution time on data-access stalls, implying that high-performance systems should focus on bringing data on chip [2, 93, 101], typically to the second-level (L2) cache found on chip in modern processors.

However, over the past decade, advancements in semiconductor technology have dramatically changed the landscape of on-chip caches. The increase in the number of transistors available on-chip has enabled on-chip cache sizes to increase exponentially across processor generations. The trend of increasing on-chip cache sizes is apparent in Figure 1 (a), which presents historic data on the on-chip cache sizes of several processors in the last two decades. The upward trend in cache sizes shows no signs of a slowdown. Industry advocates large caches as a microarchitectural technique that allows designers to exploit the available transistors efficiently to improve performance [14]. At the same time, the advent of multicore processors requires large on-chip caches to supply the ever-increasing number of on-chip cores with data. As a result, modern processors increasingly

FIGURE 1: Historic trends of on-chip caches on (a) size, and (b) latency.

feature mega-caches on chip (e.g., 16MB in Dual-Core Intel Xeon 7100 [85], and 24MB in Intel Nehalem-EX [53] and Intel Itanium 2 [104]).

Large caches, however, come at the cost of high access latency. Figure 1 (b) presents historic data on the L2 cache access latency, indicating that on-chip L2 latency has increased between 3-fold to 6-fold during the past decade — e.g., from 4 cycles in Intel Pentium III (1995) to 26 cycles in Sun UltraSPARC T2 (2007) [95]. Caches enhance performance most when they capture fully the primary working set of the workload; otherwise, they provide only marginal improvements in the miss rate as size increases. Commercial server workloads typically have a small primary working set which can be captured on chip, and a large secondary set which is beyond the reach of on-chip caches for modern processors. Conventional wisdom dictates that large on-chip caches provide significant performance benefits as they eliminate off-chip memory requests. In reality, a large cache may degrade the performance of server workloads because the cache's high latency slows the common case (cache hits) and introduces stalls in the execution, while the additional capacity fails to lower the miss rate enough to compensate. As a case study, we investigate the performance of database workloads on modern CMPs and identify data cache stalls as a fundamental performance bottleneck. Recent work in the database community [1, 2, 79] attributes most of the data stalls to off-chip memory accesses. In contrast to prior work, our results indicate that the current trend of increasing L2 latency intensifies stalls due to L2 hits<sup>1</sup>, shifting the bottleneck from off-chip accesses to on-chip L2 hits.

Thus, merely bringing data on-chip is no longer enough to attain maximum performance and sustain high throughput. Rather, it is imperative that modern CMP designs optimize for low on-chip data access latencies as well, especially to the (typically larger) last-level cache (LLC).

#### **1.2 Near-Optimal On-Chip Block Placement and Replication**

The exponential increase in the number of cores on chip results in a commensurate increase in the on-chip cache size required to supply all these cores with data. At the same time, physical and manufacturing considerations suggest that future processors will be tiled: the last-level onchip cache will be decomposed into smaller *slices*, and groups of processor cores and cache slices will be physically distributed together throughout the die area [8,107]. Tiled architectures give rise to varying access latencies between the cores and the cache slices spread across the die, naturally leading to a Non-Uniform Cache Access (NUCA) organization of the LLC, where the latency of a cache hit depends on the physical distance between the requesting core and the location of the cached data. Although increasing device switching speeds results in faster cache-bank access times, communication delay remains constant across technologies [20], and access latency of far away cache slices becomes dominated by wire delays and on-chip communication [60].

<sup>1.</sup> We refer to the time spent by the processor accessing a cache block that missed in L1D but was found in L2 as "L2 hit stalls".

An ideal LLC allows for fast access to data, large aggregate capacity to store the everincreasing applications' working sets, and has a simple and practical design. Ideally, the cache places blocks on chip close to the cores that access them. In the case of shared blocks, a mechanism is required to either place the shared blocks equally close to all sharers, or to replicate the blocks among all shares, thereby bringing them close to each one. In this thesis we propose *Reactive NUCA* (R-NUCA), a scalable, low-overhead, and low-complexity cache architecture that optimizes block placement for all cache accesses.

R-NUCA cooperates with the operating system to classify accesses at the page granularity, achieving negligible hardware overhead and avoiding complex heuristics that are prone to error, oscillation, or slow convergence [12,19,23]. The placement decisions in R-NUCA guarantee that each modifiable block is mapped to a single location in the aggregate cache, obviating the need for complex, area- and power-intensive coherence mechanisms prevalent in prior on-chip block placement proposals [12,19,23,107]. R-NUCA utilizes *Rotational Interleaving*, a novel lookup mechanism that matches the fast speed of address-interleaved lookup, without pinning blocks to a single location in the cache [23,107]. Rotational interleaving allows read-only blocks to be shared by neighboring cores and replicated at distant ones, ensuring low access latency while balancing capacity constraints. Overall, we find that R-NUCA allows for near-optimal block placement in a physically-distributed on-chip cache, attaining performance within 5% of an ideal cache design.

While it is imperative that future multicores optimize for on-chip data access latency, there are still many design decisions left to be answered. The capability of future CMPs to host exponentially larger numbers of cores do not directly translate into a commensurate increase in performance. Rather, the abundance of hardware resources comes not only at the cost of increased on-chip data access latencies, but also increased power consumption and off-chip bandwidth require-

ments. However, chips are physically constrained—cooling technology and thermal considerations limit the maximum power at almost constant levels across process technologies, manufacturing considerations and yield economics cap the maximum affordable chip size, while packaging constraints limit the number of pins and the available off-chip bandwidth. Thus, it is important that we optimize future multicore processors with all constraints in mind, in addition to performance. With a promising distributed cache design on hand, we then embark on exploring the design parameters of physically-constrained multicore processors to find the optimal designs for server workloads.

#### **1.3 Optimal CMPs Across Technologies**

Design parameters such as the number and type of cores, the supply voltage, the on-chip clock frequency, the size of the on-chip cache, and the chip's operational temperature are intertwined and affect each other non-linearly. Thus, to attain maximum performance and power-efficiency, it is imperative that all design parameters are jointly optimized to maximize their impact on performance while keeping overheads at bay.

Through first-order analytic modeling of server applications' dataset evolution, multicore performance, power, off-chip bandwidth, memory technology, and thermal constraints, we propose multicore designs for commercial server workloads that attain the highest performance at a given power budget. These models conform to ITRS projections across process technologies and jointly optimize supply and threshold voltage, on-chip clock frequency, core count and technology, cache size, and memory technology to result in multicore designs that lie on the pareto frontier of peak-performance designs. We find that ideal future multicores will be based on heterogeneous cores built with low-operational-power devices, employ large multi-megabyte caches, utilize 3D-die

stacking to alleviate the pin bandwidth limitations, and rely on novel on-chip data placement mechanisms that encourage localized data transfers.

#### **1.4 Contributions**

In this thesis we investigate multicore designs for commercial server workloads. Through a combination of analytic modeling, execution trace analysis and cycle-accurate full-system simulation using FLEXUS [42,103] of multicore processors running a range of unmodified commercial server applications and multiprogrammed workloads, we demonstrate:

- On-chip cache latency dominates execution time. The large on-chip cache sizes of modern CMPs and the high levels of data sharing in commercial workloads increase the cache hit rate, but the higher data access latencies penalize each hit with extra cycles. The combined effects result in server workloads spending up to 35% of their execution time stalled on cache hits, amounting to an increase on the time spent in the on-chip cache by a factor of 5-7 over traditional symmetric multiprocessors.

- **On-line classification of cache accesses**. We show that cache accesses in server workloads can be classified at run time into classes that exhibit distinct characteristics, leading to different on-chip cache block placement policies.

- **Reactive NUCA**. We leverage the characteristics of each access class to design Reactive NUCA (R-NUCA), a low-overhead, low-latency mechanism for block placement in distributed caches. R-NUCA improves performance by allocating cache blocks close to the cores that access them, replicating or migrating them as necessary without the overhead of a hardware coherence mechanism.

- Rotational Interleaving. To make block replication practical, we propose Rotational Interleaving, a mechanism for fast lookup in distributed caches with replicated blocks. Rotational Interleaving enables cache block replication in the distributed cache without wasting space and without coherence overheads. It balances capacity constraints with access latency by distributing blocks to nearest neighbors to relieve capacity pressure and ensuring that all allocation decisions among neighbors are mutually consistent, while indexing blocks by always probing only the cache slice that may have the requested block (single-probe lookup). Thus, it provides lookup speeds comparable to conventional address interleaving, without pinning blocks to a single location in the cache.

- **Performance Robustness**. We find that R-NUCA provides performance stability across workloads, as on a per-workload basis it either matches the performance of competing cache designs or improves upon them by 17% on average and by 32% at best, while performing within 5% of an ideal design.

- **CMP Design-Space Exploration Across Process Technologies**. We explore the design space of physically-constrained CMPs across technologies and find that heterogeneous multicores is a viable alternative that holds great promise in optimizing the chip design. Contrary to conventional wisdom, we find that the cores can be implemented using low-operational-power devices without loss in performance, but with significant reduction in power. In contrast to prior research findings, we find that 3D-stacked memory can mitigate the bandwidth wall, making peak-performance designs purely power-constrained. Finally, we find that cache sizes will continue to grow at an exponential rate, so future multicore processors will require novel on-chip data placement mechanisms that encourage localized data transfers.

The rest of the thesis is organized as follows. In Chapter 2, we analyze the performance of chip multiprocessors running database workloads as a case study that quantifies the impact of modern hardware trends on commercial server workloads. In Chapter 3, we introduce Reactive NUCA and Rotational Interleaving and evaluate their performance. In Chapter 4, we introduce first-order analytical models that we use to explore the design space of physically-constrained multicore processors across technologies. We comment on related research in Chapter 5 and conclude in Chapter 6.

The performance analysis in Chapter 2 was previously presented in CIDR 2007 [41]. The Reactive NUCA and Rotational Interleaving designs in Chapter 3 were previously presented in ISCA 2009 [40]. In this document, we provide a more detailed description of Reactive NUCA and Rotational Interleaving that was not possible in the limited space of a conference publication. Material presented in Chapter 4 has not yet appeared in other venues.

# Chapter 2

## Performance Analysis of CMPs

#### **2.1 Introduction**

The commercial server market forms a multi-billion dollar industry [36,37] that penetrates deeply into our everyday life, from ATM and credit card transactions, to travel, to commerce, to government services. High-end servers employ state-of-the-art processors and software to maximize performance. Any failure to realize their maximum potential directly translates into lost investment and impacts the end user who demands low response times and high availability at minimum cost. At the same time, improving the performance of commercial server software will free computational resources for additional services besides the absolutely necessary for a transaction (e.g., it will allow augmenting transactions with on-line fraud detection). Unfortunately, current technological trends make it increasingly difficult to attain high processor utilization and reach maximum performance.

While prior research advocates that high-end server systems and software should focus on bringing data on chip to mitigate the processor-memory performance gap [2], the advent of multicore processors has resulted in an exponential increase in cache sizes and on-chip interconnects which shift the dominant performance bottlenecks. Large caches and interconnects come at the expense of slow on-chip data access times, which increases the contribution of on-chip cache hits to execution time. At the same time, the relative contribution of off-chip accesses to execution time dwindles as clock frequency increases have stagnated [7] and DRAM access latency continues to improve. Additionally, multicore processors may increase processor stalls through promoting on-chip data sharing across cores and increasing contention for shared hardware resources.

In this study, we quantify the effects of current hardware trends on the performance of commercial server workloads using database applications as a case study. We demonstrate that the growing L2 hit latency largely determines the performance of commercial software servers. In essence, server workloads are running into an "on-chip cache wall", which has become the new fundamental bottleneck. Our results present a departure from prior research findings that identify off-chip accesses as the dominant barrier to high performance [2, 1, 79]. In contrast to prior work, our results indicate that the current trend of increasing L2 latency intensifies stalls due to L2 hits<sup>1</sup>, shifting the bottleneck from off-chip accesses to on-chip L2 hits. Thus, merely bringing data onchip is no longer enough to attain maximum performance and sustain high throughput.

In this study we recognize that chip multiprocessor designs follow two distinct schools of thought, and present a taxonomy of processor designs and DBMS workloads to distinguish the various combinations of workload and system configuration. We divide chip multiprocessors into two "camps." The *fat camp* employs wide-issue out-of-order processors and addresses data stalls by exploiting instruction-level parallelism (e.g., Intel Core Duo [52], IBM Power 5 [57]). The *lean camp* employs heavily multithreaded in-order processors to hide data stalls across threads by overlapping data access latencies with useful computation (e.g., Sun UltraSPARC T1 [61]). Even though LC is heavily multithreaded, it is a much simpler hardware design than the complex out-of-order FC. We divide database applications into *saturated* workloads, in which idle processors

<sup>1.</sup> We refer to the time spent by the processor accessing a cache block that missed in L1D but was found in L2 as "L2 hit stalls".

always find an available thread to run, and *unsaturated* workloads, in which processors may not always find threads to run, thereby exposing data access latencies. We characterize the performance of each database workload and system configuration pair within the taxonomy through cycle-accurate full-system simulations using FLEXUS [42,103] of on-line transactional processing (OLTP) and decision support system (DSS) workloads on a commercial DBMS. Our results indicate that:

- High on-chip cache latencies shift the data stall component from off-chip data accesses to L2 hits, to the point where up to 35% of the execution time is spent on L2 hit stalls for our work-load and CMP configurations. The increased cache latency results in workloads losing as much as half of their potential performance.

- High levels of on-chip core integration increase L2 hit rates, improving performance by 12-15% and increasing the relative contribution of L2 hit stalls to 10% and 25% of execution time, respectively, for DSS and OLTP.

- The combined effects of high L2 latency and higher L2 hit rates due to on-chip core integration increase the contribution of L2 hit stalls on execution time by a factor of 5 for DSS and a factor of 7 for OLTP over traditional symmetric multiprocessors, explaining the observed departure from prior research findings.

Conventional DBMS hide stalls only in one out of four combinations of chip designs and work-loads. Despite the significant performance enhancements that stem from chip-level parallelism, the fat camp still spends 46-64% of execution time on data stalls. The lean camp efficiently overlaps data stalls when executing saturated workloads, but exhibit up to 70% longer response times than the fat camp for unsaturated workloads.

The remainder of this chapter is structured as follows. Section 2.2 proposes a taxonomy of chip multiprocessor technologies and workloads. Section 2.3 presents our experimental methodology and Section 2.4 analyzes the behavior of a commercial database server on chip multiprocessors, as a function of hardware designs and workloads. Section 2.5 discusses the effects of hardware parameters on data stalls. Finally, Section 2.6 presents a summary of our analysis.

#### 2.2 CMP Camps and Workloads

In this section we propose a taxonomy of chip multiprocessor technologies and database workloads, and analyze their characteristics. To our knowledge, this is the first study to provide an analytic taxonomy of the behavior of database workloads in such a diverse spectrum of current and future chip designs. A recent study [30] focuses on throughput as the primary performance metric to compare server workload performance across chip multiprocessors with varying processor granularity, but has stopped short of a detailed performance characterization and breakdown of where time is spent during execution. The taxonomy we propose enables us to concentrate on each segment separately and derive the reasons behind our performance observations. Through a series of simulations we find that the behavior of database systems varies as a function of hardware and workload type, and that conventional database systems fail to provide high performance across the entire spectrum.

| Core Technology  | Fat Camp (FC)      | Lean Camp (LC)       |

|------------------|--------------------|----------------------|

| Issue Width      | Wide (4+)          | Narrow (1 or 2)      |

| Execution Order  | Out-of-order       | In-order             |

| Pipeline Depth   | Deep (14+ stages)  | Shallow (5-6 stages) |

| Hardware Threads | Few (1-2)          | Many (4+)            |

| Core Size        | Large (3 x LCsize) | Small (LC size)      |

Table 1: Chip multiprocessor camp characteristics.

#### 2.2.1 Fat Camp vs. Lean Camp

Hardware vendors adopt two distinct approaches to chip multiprocessor design. One approach uses cores that target maximum single-thread performance through sophisticated out-of-order execution and aggressive speculation (fat-camp or FC). Representative chip multiprocessors from this camp include Intel Core Duo [52] and IBM Power5 [57]. The second approach favors much simpler designs with cores that support many thread contexts<sup>1</sup> in hardware (lean-camp or LC). Such cores overlap stalls in a given thread with useful computation by other threads. Sun UltraSPARC T1 [61] and Compaq Piranha [10] fall into this camp. Table 1 summarizes the characteristics of each technology camp.

Integrating multiple cores on a chip multiprocessor exhibits similar effects within each camp (e.g., increase in shared resource contention). In this chapter we study the increasing performance differences between fat and lean camps when running identical database workloads, assuming that both camps are supported by the same memory hierarchy. Thus, it suffices to analyze the characteristics of each camp by focusing on the characteristics of the different core technologies within each camp.

<sup>1.</sup> We refer to hardware threads as "hardware contexts" to distinguish them from software (operating system) threads.

Because LC cores are heavily multithreaded, we expect them to hide stalls efficiently and provide high and scalable throughput when there is enough parallelism in the workload. However, when the workload consists of a few threads, the LC cores cannot find enough threads to overlap stalls, leaving long data access latencies exposed. On the other hand, the FC cores are optimized for single-thread performance through wide pipelines that issue/complete multiple instructions per cycle, and out-of-order speculative execution. These features exploit instruction-level parallelism within the workload to hide stalls.

Thus, we expect LC cores to outperform FC cores when there is enough parallelism in the workload, even with much lower single-thread performance than that of an FC core. However, when the workload consists of few threads, we expect the response time of the single-thread optimized FC cores to be significantly lower than the corresponding response time of their LC counterparts.

In addition to the performance differences when comparing single cores, an LC CMP can typically fit three times more cores in one chip than an FC CMP, resulting in roughly an order of magnitude more hardware contexts in the same space. In this study we do not apply constraints on the chip area. Keeping a constant chip area would favor the LC camp because it would have a larger on-chip cache than the FC camp, allowing LC to attain even higher performance in heavily multithreaded workloads, because LC is able to hide L2 stalls through multithreading.

#### 2.2.2 Unsaturated vs. Saturated Workloads

Database performance varies with the number of requests serviced. Our unsaturated workload highlights single-thread performance by assigning one worker thread per query (or transaction) it receives. A conventional DBMS can increase the parallelism through partitioning, but in

FIGURE 2: Unsaturated vs. saturated workloads.

the context of this study we can treat this as having multiple clients (instead of threads). The reader should also keep in mind that not all query plans are trivially parallelizable.

We observe that the performance of a database application falls within one of two regions, for a given hardware platform, and characterize the workload as unsaturated or saturated. A workload is unsaturated when processors do not always find threads to run. As the number of concurrent requests increases, performance improves by utilizing otherwise idle hardware contexts. Figure 2 illustrates throughput as a function of the number of concurrent requests in the system when running TPC-H queries on a commercial DBMS on a real 4-core IBM Power5 (FC) server. Increasing the number of concurrent requests eventually results in a saturated workload, where there are always available threads for idle processors to run. Peak performance occurs at the beginning of the saturated region; increasing the number of concurrent requests too far overwhelms the hardware, reducing the amount of useful work performed by the system and lowering performance.

#### 2.3 Experimental Methodology

We use FLEXUS [42,103] to provide accurate simulations of chip multiprocessors and symmetric multiprocessors running unmodified commercial database workloads. FLEXUS is a cycleaccurate full-system simulator that simulates both user-level and operating system code. We use the SimFlex statistical sampling methodology [103]. Our samples are drawn over an interval of 10 to 30 seconds of simulated time (as observed by the operating system in functional simulation) for OLTP, and over the complete workload execution for DSS. We show 95% confidence intervals on performance measurements using paired measurement sampling. We launch measurements from checkpoints with warmed caches and branch predictors, then run for 100,000 cycles to warm queue and interconnect state prior to collecting measurements of 50,000 cycles. We use the aggregate number of user instructions committed per cycle (i.e., committed user instructions summed over the simulated processors divided by total elapsed cycles) as our performance metric, which is proportional to overall system throughput [103].

We characterize the performance of database workloads on an LC CMP and an FC CMP with the UltraSPARC III instruction set architecture running the Solaris 8 operating system. The LC CMP employs four 2-issue superscalar in-order cores. The LC cores are 4-way multithreaded, for a total of 16 hardware contexts on the LC CMP. The hardware contexts are interleaved in round-robin fashion, issuing instructions from each runnable thread in turn. When a hardware context stalls on a miss it becomes non-runnable until the miss is serviced. In the meantime, the LC core executes instructions from the remaining contexts.

The FC CMP employs four aggressive out-of-order cores that can issue four instructions per cycle from a single hardware context. The two CMP designs have identical memory subsystems

and clock frequencies and feature a shared on-chip L2 cache with size that ranges from 1MB to 26MB.

We estimate cache access latencies using Cacti 5.3 [97]. Cacti is an integrated cache access time, cycle time, area, leakage, and dynamic power model. By integrating all these models together, cache trade-offs are all based on the same assumptions and, hence, are mutually consistent. In some experiments we purposefully vary the latency of caches beyond the latency indicated by Cacti to explore the resulting impact on performance or to obtain conservative estimates.

Our workloads consist of OLTP (TPC-C) and DSS (TPC-H) benchmarks running on a commercial DBMS. The saturated OLTP workload consists of 64 clients submitting transactions on a 100-warehouse database. The saturated DSS workload consists of 16 concurrent clients running four queries from the TPC-H benchmark, each with random predicates. We select the queries as follows [88]: Queries 1, 6 are scan-dominated, Query 16 is join-dominated and Query 13 exhibits mixed behavior. To achieve practical simulation times we run the queries on a 1GB database. We corroborate recent research that shows that varying the database size does not incur any microarchitectural behavior changes [88]. Unsaturated workloads use the above methodology running only a single client, with intra-query parallelism disabled to highlight single-thread performance. We tune both the OLTP and DSS workloads to minimize I/O overhead and maximize CPU and memory system utilization.

FIGURE 3: validation using the saturated DSS workload.

We validate by comparing against an IBM OpenPower720 server that runs the same workloads. We calculate the cycles per instruction (CPI) on OpenPower720 by extracting Power5's hardware counters through pmcount [27], post-processing the raw counters using scripts kindly provided by IBM, and comparing the results with a simulation that approximates the same IBM server. Figure 3 presents the absolute CPI values and their respective breakdowns. The overall simulated CPI is within 5% of the measured CPI for both OLTP and DSS workloads. The computation component for OpenPower720 is 10% higher, which we attribute to Power5's instruction grouping and cracking overhead. The data stall component is 15% higher due to the absence of a hardware prefetcher mechanism.

While employing a stride prefetcher will not change the performance trends that are the focus of our study, it is instructive to discuss its performance implications on our workload mix. Prior research [93] measures the impact of hardware prefetching on the performance of OLTP and DSS workloads and finds that even complex hardware prefetchers that subsume stride prefetchers yield less than 10% performance improvement for OLTP workloads and scan-dominated DSS queries. Join-dominated DSS queries do see as much as 50% improvement, but contribute relatively

little to total execution time in our DSS query mix. Even if a stride prefetcher could match the performance improvements of [93], we estimate that the performance improvement due to a stride prefetcher on our OLTP workload will be less than 10%, while the performance improvement on our scan-dominated DSS workload will be less than 20%. However, the performance trends due to the increasing L2 latencies will remain the same.

# 2.4 DBMS Performance on CMPs

In this section we characterize the performance of both CMP camps on a commercial DBMS running unsaturated and saturated DSS and OLTP workloads. For unsaturated workloads the performance metric of interest is response time, while for saturated workloads the performance metric of interest is throughput. Figure 4 (a) presents the response time of the LC CMP normalized to the FC CMP when running unsaturated (single-thread) workloads. Figure 4 (b) presents the throughput of the LC CMP normalized to the throughput of the LC CMP normalized to the throughput of the FC CMP when running saturated workloads.

The LC CMP suffers up to 70% higher response times than FC when running unsaturated (single-thread) DSS workloads and up to 12% higher when running unsaturated OLTP workloads, corroborating prior results [79]. The performance difference between FC and LC on unsaturated OLTP workloads is narrower due to limited ILP. Even though FC exhibits higher single-thread per-

FIGURE 4: (a) Response time and (b) throughput of LC normalized to FC.

formance than LC, the LC CMP achieves 70% higher throughput than its FC counterpart when running saturated workloads (Figure 4 b).

Figure 5 shows the execution time breakdown for each camp and workload combination. Although we configure the CMPs with an unrealistically fast 26MB shared L2 cache, data stalls dominate execution time in three out of four cases. While FC spends 46% - 64% of execution time on data stalls, LC spends at most 13% of execution time on data stalls when running saturated workloads, while spending 76-80% of the time on useful computation. The multiple hardware contexts in LC efficiently overlap data stalls with useful computation, thereby allowing LC to outperform significantly its FC counterpart on saturated workloads.

Despite prior work [2] showing that instruction stalls often dominate memory stalls when running database workloads, our CMP experiments indicate that data stalls dominate the memory access component of the execution time for all workload/camp combinations. Both camps employ instruction stream buffers [56], a simple hardware mechanism that automatically initiates

FIGURE 5: Breakdown of execution time.

prefetches to successive instruction cache lines following a miss. Our results corroborate prior research [79] that demonstrates instruction stream buffers efficiently reduce instruction stalls. Because of their simplicity, instruction stream buffers can be employed easily by the majority of chip multiprocessors, thus we do not further analyze instruction cache performance.

We conclude that the abundance of threads in saturated workloads allows LC CMPs to hide data stalls efficiently. The multiple hardware contexts available on the LC CMP allow it to perform useful computation while some of the contexts are stalled on long latency data access operations, thereby improving overall throughput. In contrast, the FC CMP fails to utilize fully its hardware resources because database workloads exhibit limited ILP. FC processors would also benefit from multithreaded operation, but their complexity limits the number of hardware contexts they can employ. Our calculations show that each FC core would require more than 15 hardware contexts to fully overlap data stalls, which is infeasible due to the complexity and power implications it entails. Thus, FC CMPs cannot hide data stalls the way context-rich LC CMPs can.

However, we expect that in spite of less than ideal performance on database workloads, FC CMPs will still claim a significant market share due to their unparalleled single-thread performance and optimized execution on a variety of other workloads (e.g., desktop, scientific computing). Thus, database systems must be designed to perform well on both CMP camps, independent of workload type. To maximize performance across hardware and workload combinations, database systems must exhibit high thread-level parallelism across and within queries and transactions, and improve data locality/reuse. Increased parallelism helps exploit the abundance of on-chip thread and processor execution resources when the workload is not saturated. Data locality helps eliminate stalls independent of workload type.

Figure 5 shows that in six out of eight combinations of hardware and workloads, data stalls dominate execution time even with unrealistically fast and large caches. In Section 2.5 we analyze the data stall component of execution time to identify dominant subcomponents and trends, that will help guide the implementation and optimization of future database software. In the interest of brevity, we analyze data stalls by focusing on saturated database workloads running on FC CMPs, but the results of our analysis are applicable across all combinations of hardware and workloads that exhibit high data stall time.

# 2.5 Analysis of Data Stalls

In this section we analyze the individual sub-components of data cache stalls and identify the emerging importance of L2 hit stalls, which account for up to 35% of execution time for our hardware configurations and workloads. This represents a a 7-fold increase as compared to traditional symmetric multiprocessors with small caches running the same workloads.

FIGURE 6: Effect of cache size and latency on throughput.

Section 2.5.1 explores the impact of increased on-chip cache sizes on the breakdown of data stalls. In Section 2.5.2 we analyze the impact of moving from traditional (multi-chip) multiprocessors to single-chip multiprocessors. Finally, in Section 2.5.3 we study the effects of high levels of on-chip core integration.

# 2.5.1 Impact of On-Chip Cache Size

Large on-chip L2 caches shift the data stall bottleneck in two ways. First, large caches exhibit high hit rates. As more requests are serviced by the cache, data stalls shift from memory to L2 hits. Second, rising hit latencies penalize each hit and increase the number of stalls caused by L2 hits without changing the number of accesses to other parts of the memory hierarchy.

Figure 6 presents the impact of increasing cache size on DBMS performance. We simulate both OLTP and DSS workloads on a FC CMP, with cache sizes ranging from 1MB to 26MB. To separate the effect of hit rates from that of hit latencies, we perform two sets of simulations. The upper (dotted) pair of lines shows the performance increase achieved when the hit latency remains

FIGURE 7: Effect of cache size and latency on CPI for (a) OLTP and (b) DSS.

fixed at an unrealistically low 4 cycles. The lower (solid) pair of lines shows the performance under the more reasonable hit latencies estimated using CACTI for each cache configuration. These estimates are conservative because hit latencies estimated by CACTI are typically lower than the ones achieved in commercial products.

In all cases, increasing the cache size significantly improves performance as more of the primary L2 working set fits in the cache. However, the realistic-latency and constant-latency performance curves quickly begin to diverge, even before the cache captures a significant fraction of the entire working set. Even though there is no cycle penalty for increasing L2 sizes in the constantlatency case, we see diminishing returns because even the biggest cache fails to capture the large secondary L2 working set. In contrast, realistic hit latencies further reduce the benefit of larger caches, and the added delay begins to outweigh the benefits of lower miss rates. The adverse effects of high L2 hit latency reduce the potential performance benefit of large L2 caches by up to 2.2x for OLTP and 2x for DSS.

FIGURE 8: CPI breakdown with increasing L2 size.

Figure 7 (a) and (b) show the effect of realistic L2 hit latencies and sizes to L2 hit stalls, memory stalls and overall CPI for OLTP and DSS respectively. In the constant-latency case (not shown) the stall component due to L2 hits quickly stabilizes at less than 5% of the total CPI. On the other hand, realistic L2 latencies are responsible for a growing fraction of L2 hit stalls to the overall CPI, especially in DSS, where they become the single largest component of execution time. Conversely, the larger L2 sizes cause a decrease in off-chip requests, with a subsequent reduction of memory stalls. These figures demonstrate that the growing L2 sizes result in L2 hits contributing significantly to execution time, while the contribution of off-chip memory requests drops.

The remainder of the CPI increase comes from instruction stalls due to L2 hits, again an artifact of larger (and slower) caches. Instruction stalls due to L2 are especially evident in the OLTP workload, where they account for roughly half of the overall CPI increase. This is evident in Figure 8 which shows the breakdown of CPI for OLTP and DSS with increasing cache size.

Increasing cache sizes and their commensurate increase in latency can have dramatic effects on the fraction of time spent on L2 hit data stalls. For our workloads running on a FC CMP we

FIGURE 9: Impact of chip multiprocessing on CPI.

measure a 12-fold increase in time spent in L2 hit stalls when increasing the cache size from 1MB to 26MB; rising hit latencies are responsible for up to 78% of this increase.

# 2.5.2 Impact of Core Integration on Single Chip

In this section we study the outcome of integrating multiple processing cores on a single chip. We compare the performance of a commercial database server running OLTP and DSS work-loads in two variants of our baseline system: (a) a 4-processor SMP with private 4MB L2 caches at each node, and (b) a 4-core CMP with a single shared 16MB L2.

Figure 9 presents normalized CPI breakdowns for the two systems, with labels indicating the actual CPI. We observe that the performance of the CMP systems is higher. The difference in the performance between the SMP and the CMP systems can be attributed to the elimination of coherence traffic. Data accesses that result in long-latency coherence misses in the SMP system are converted into L2 hits on the shared L2 cache of the CMP and fast L1-to-L1 on-chip data transfers. Thus, the L2 hit stall component of CPI increases by a factor of 7 over the corresponding SMP designs, explaining the disparity of our results as compared to prior research findings [2,88].

FIGURE 10: Impact of core count on (a) throughput, and (b) CPI breakdown.

# 2.5.3 Impact of On-Chip Core Count

Chip multiprocessors integrate multiple cores on a single chip, which promotes sharing of data through the common L2 cache. At the same time, contention for shared hardware resources my offset some of the benefits of fast on-chip data sharing. To study the impact of high levels of core integration on chip we simulate saturated OLTP and DSS workloads on a FC chip multiprocessor with a 16MB shared L2 as we increase the number of cores from 4 (the baseline) to 16.

Figure 10(a) presents the change in performance as the number of processing cores increases. The diagonal line shows linear speedup as a reference. We observe a 9% super-linear increase in throughput at 8 cores for DSS, due to an increase in sharing, after which pressure on the L2 cache adversely affects performance for both workloads. OLTP, in particular, realizes about 74% of its potential linear performance improvement. The pressure on the cache is not due to extra misses — in fact, the L2 miss rate continues to drop due to increased sharing as more cores are added. Rather, physical resources such as cache ports and status registers induce queueing delays

during bursts of misses. These correlated misses are especially common in OLTP and are largely responsible for the sub-linear speedup when adding more cores.

Figure 10(b) shows the CPI breakdown of a CMP running our OLTP and DSS workloads as the core count increases. The breakdown shows that the contribution of instruction stalls for OLTP increases dramatically with increasing core count. This increase is due to contention for the instruction cache blocks. As we will see in the next chapter, the instruction stream for commercial server workloads is universally shared among all cores, so the introduction of more cores does not result in more misses; on the contrary, the hit rate for instructions increases as all cores request the same blocks. However, the increased contention for instruction blocks creates hot spots in the cache, causing the cores to queue their requests behind others already in the cache controller and stall until the requests can be serviced. This observation shows that while it is important for future multicore architectures to alleviate the growing on-chip cache access latency, it is also important to invent techniques that will reduce contention for hot cache blocks.

# 2.5.4 Ramifications

Our analysis of data stalls and the impact of current hardware trends on CMP performance have several ramifications. The bottleneck shift to L2 hit stalls arises primarily from the combination of higher L2 hit rates, increased L2 hit latencies and increased cache block contention due to on-chip core integration. The emerging L2 hit stalls indicate that simply bringing data on chip no longer suffices to attain maximum performance. In the future it will become increasingly important to utilize techniques that lower the L2 access latency. This will be our focus in Chapter 3.

The growing L2 hit latencies can be alleviated by bringing data beyond L2 and closer to L1, for example through streaming and prefetching. Several streaming and prefetching techniques

have been proposed by the architectural community [55,78,93,101,21,48,83,90,99,92,59, 102,70,72,84,71], where complicated hardware, the compiler or a hardware/software mechanism strive to recognize the workloads' access patterns and stream data ahead of the request. However, these techniques typically focus on predicting off-chip requests, where the large size and relative inactivity of L2 make them tolerable to mispredictions, and the processor-memory gap provides a large opportunity for improvement. In on-chip streaming, however, the small L1s and stream buffers are prone to pollution, and the L1-to-L2 distance is relatively small, so none but the most accurate techniques may effectively stream blocks within a chip. Unfortunately, commercial server workloads exhibit adverse and arbitrarily complex data sharing and access patterns [21,94,101] that hamper most efforts to build prefetching engines that attain both high accuracy and coverage.

Second, increasing the number of cores that share an on-chip L2 cache does not cause an inordinate number of additional cache misses for commercial server workloads. In fact, these workloads exhibit significant sharing, so the cores benefit from each other's requests (constructive interference). However, the extra cores do cause contention for hot blocks that can degrade performance in spite of the lower miss rate. We expect that future CMP designs will feature specially-designed L2 caches to reduce this pressure, allowing workloads to benefit from the effects of sharing. Our proposed cache design in Chapter 3 also helps alleviate most of the cache block contention by replicating the hottest blocks across the die area.

Third, incorporating large (slow) caches on chip can have detrimental effects to the performance of commercial server workloads. Optimized future CMP designs should incorporate caches large enough to capture the primary L2 working set, but not larger, so they can maintain reasonably low hit latencies. This observation runs counter to the conventional wisdom that larger caches are always a good way to use extra transistors [14]. We will investigate the trade-off between hit rate and cache access latency through first-order analytic modeling of CMPs in Chapter 4.

Finally, the software system can be restructured to intelligently balance parallelism with locality and work synergistically with hardware. Conventional software is optimized for outdated hardware architectures, assuming private resources and coarse-grain OS-managed threads with no coordination of resource usage among them. However, modern CMPs employ shared hardware resources and facilitate fine-grain communication between software threads. To utilize efficiently the available hardware resources, modern software systems can be restructured to split otherwise single-threaded operations into many smaller parallel tasks, and simultaneously optimize for data affinity to processors to minimize cross-chip data transfers. Such software architectures can expose the data access and sharing patterns to the execution system, allowing simple hardware techniques to eliminate the remaining on-chip data access stall times. We will discuss our current efforts in this area when we present future work in Chapter 6.

# 2.6 Summary

High levels of integration have enabled the advent of chip multiprocessors and increasingly large (and slow) on-chip caches. These trends of increasing core counts and larger on-chip caches pose new performance challenges to the architecture and software communities. In this study we present a performance characterization of a commercial database servers in a number of representative chip multiprocessor technologies. Our results indicate that on-chip cache accesses are the new performance bottleneck, with L2 hit stalls rising from oblivion to become the dominant single execution time component. Future processors must employ novel cache architectures that keep access latency and block contention at bay without sacrificing capacity. At the same time, software

systems and not ready for such dramatic shifts in hardware design and must be restructured to utilize efficiently the new hardware.

In the next chapter, we introduce Reactive NUCA, our proposal for a novel distributed cache architecture that allows for fast access and low contention for hot cache blocks by placing blocks on chip close to the cores that access them. Later, in Chapter 6, we present our on-going work on novel software architectures that enhance parallelism and locality, and show promise in utilizing efficiently the hardware resources of modern multicore processors.

# Chapter 3 Reactive NUCA

The exponential increase in the number of cores on chip results in a commensurate increase in the on-chip cache size required to supply all these cores with data and the on-chip interconnect that facilitates cross-chip data transfers. At the same time, physical and manufacturing considerations suggest that future processors will be tiled: the last-level on-chip cache will be decomposed into smaller *slices*, and groups of processor cores and cache slices will be physically distributed throughout the die area [8,107].

Tiled architectures result in varying access latencies between the cores and the cache slices spread across the die, as the latency of a cache hit depends on the physical distance between the requesting core and the location of the cached data. Although increasing device switching speeds results in faster cache-bank access times, communication delay remains constant across technologies [20], and access latency of far away cache slices becomes dominated by wire delays and on-chip communication [60]. Thus, tiled architectures naturally lead to a Non-Uniform Cache Access (NUCA) [60] organization of the LLC.

From an access-latency perspective, an LLC organization where each core treats a nearby LLC slice as a private cache is desirable. Although a private organization results in fast local hits, it requires area-intensive, slow and complex mechanisms to guarantee the coherence of shared data, which are prevalent in many multicore workloads [11,41]. At the same time, the growing

application working sets render private caching designs impractical due to the inefficient use of cache capacity, as cache blocks are independently replicated in each private cache slice.

At the other extreme, a shared organization where blocks are statically address-interleaved in the aggregate cache offers maximum capacity by ensuring that no two cache frames are used to store the same block. Because static interleaving defines a single, fixed location for each block, a shared LLC does not require a coherence mechanism, enabling a simple design and allowing for larger aggregate cache capacity. However, static interleaving results in a random distribution of cache blocks across the LLC slices, leading to frequent accesses to distant cache slices and high average access latency.

An ideal LLC enables the fast access of the private organization and the design simplicity and large capacity of the shared organization. Recent research advocates hybrid and adaptive mechanisms to bridge the gap between the private and shared organizations. However, prior proposals require complex, area-intensive, and high-latency lookup and coherence mechanisms [12,19,23,107], waste cache capacity [12,107], do not scale to high core counts [19,39], or optimize only for a subset of the cache accesses [12,19,24]. In this thesis we propose *Reactive NUCA* (R-NUCA), a scalable, low-overhead, and low-complexity cache architecture that optimizes block placement for all cache accesses, at the same time attaining the fast access of the private organization and the large aggregate capacity of the shared organization.

R-NUCA cooperates with the operating system to classify accesses at the page granularity, achieving negligible hardware overhead and avoiding complex heuristics that are prone to error, oscillation, or slow convergence [12,19,23]. The placement decisions in R-NUCA guarantee that each modifiable block is mapped to a single location in the aggregate cache, obviating the need for complex, area- and power-intensive coherence mechanisms of prior proposals [12,19,23,107].

R-NUCA utilizes *Rotational Interleaving*, a novel lookup mechanism that matches the fast speed of address-interleaved lookup, without pinning blocks to a single location in the cache [23,107]. Rotational interleaving allows read-only blocks to be shared by neighboring cores and replicated at distant ones, ensuring low access latency while balancing capacity constraints.

The work presented in this chapter makes the following contributions:

- Through execution trace analysis, we show that cache accesses for instructions, private data, and shared data exhibit distinct characteristics, leading to different replication, migration, and placement policies.

- We leverage the characteristics of each access class to design R-NUCA, a novel, low-overhead, low-latency mechanism for block placement in distributed caches.

- We propose rotational interleaving, a novel mechanism for fast nearest-neighbor lookup with one cache probe, enabling replication without wasted space and without coherence overheads.

- Through full-system cycle-accurate simulation of multicore systems, we show that R-NUCA provides performance stability across workloads. On a per-workload basis, R-NUCA either matches the performance of competing cache designs or improves upon them by 17% on average. More specifically, R-NUCA attains a maximum speedup of 32%, and an average speedup of 14% across all workloads over the private design (17% for server workloads) and 6% over the shared design (17% for multi-programmed workloads and OLTP), while achieving performance within 5% of an ideal cache design.

The rest of this chapter is organized as follows. Section 3.1 presents background on distributed caches and tiled architectures. Section 3.2 presents our classification and offers a detailed empirical analysis of the cache-access patterns of server, scientific, and multi-programmed workloads. We describe R-NUCA in Section 3.3 and evaluate it in Section 3.4. We summarize our findings in Section 3.5.

# 3.1 Background

#### **3.1.1 Non-Uniform Cache Architectures**

The exponential increase in the cache sizes of multicore processors (CMPs) renders uniform access latency impractical, as capacity increases also increase access latency [41]. To mitigate the rising access latency, recent research [60] advocates decomposing the cache into slices. Each slice may consist of multiple banks to optimize for low access latency within the slice [13], and all slices are physically distributed on the die. Thus, cores realize fast accesses to nearby slices and slower accesses to physically distant ones.

Just as cache slices are distributed across the entire die, processor cores are similarly distributed. Economic, manufacturing, and physical design considerations [8,107] suggest *tiled architectures*, with cores coupled together with cache slices in tiles that communicate via an on-chip interconnect. Tiled architectures are attractive from a design and manufacturing perspective, enabling developers to concentrate on the design of a single tile and then replicate it across the die [8]. They are also economically attractive, as they can easily support families of products with varying number of tiles and power/cooling requirements. Finally, their scalability to high core counts make them suitable for large-scale CMPs.

FIGURE 11: Typical tiled architecture and floorplan of folded 2D-torus.

## **3.1.2 Tiled Architectures**

Figure 11 presents a typical tiled architecture. Multiple tiles, each comprising a processor core, caches, and network router/switch, are replicated to fill the die area. Each tile includes private L1 data and instruction caches and an L2 cache slice. Each L1 cache miss probes an on-chip L2 cache slice via an on-chip network that interconnects the tiles. Depending on the L2 organization, the L2 slice can be either a private L2 cache or a portion of a larger distributed shared L2 cache. Also depending on the cache architecture, the tile may include structures to support cache coherence such as L1 duplicate tags [10] or sections of the L2-cache distributed directory. The tiles are connected through an on-chip folded 2D-torus interconnect.

**Private L2 organization.** Each tile's L2 slice serves as a private second-level cache for the tile's core. Upon an L1 miss, the L2 slice located in the same tile is probed. On a write miss in the local L2 slice, the coherence mechanism (a network broadcast or access to an address-interleaved

distributed directory) invalidates all other on-chip copies. On a read miss, the coherence mechanism either confirms that a copy of the block is not present on chip, or it obtains the data from an existing copy. With a directory-based coherence mechanism, a typical coherence request is performed in three network traversals. A similar request in token-coherence [73] requires a broadcast followed by a response from the farthest tile.

Enforcing coherence requires large storage and complexity overheads. For example, a fullmap directory for a 16-tile CMP with 64-byte blocks, 1MB L2 slices, and 64KB split I/D L1 caches requires 288K directory entries, assuming two separate hardware structures to keep the L1 caches and the L2 slices coherent (on each request, both structures are searched in parallel). With a 42-bit physical address space, and a 16-bit sharers bit-mask and 5-bit state per block to account for intermediate states, the directory size per tile is 1.2MB, exceeding the L2 capacity. Thus, full-map directories are impractical for the private L2 organization. Limited-directory mechanisms are smaller, but may require complex, slow, or non-scalable fall-back mechanisms such as full-chip broadcast. In this work, we optimistically assume a private L2 organization where each tile has a full-map directory with zero area overhead.