# Towards a Reconfigurable Nanocomputer Platform

|             |           | ampi arity $\rightarrow$ | e man              | oscale           |                    | ces                  |

|-------------|-----------|--------------------------|--------------------|------------------|--------------------|----------------------|

|             | Silicon   | Hetero-<br>junction      | Nanotube           | Molecular        | Magnetic           | Q-Well               |

| ← Diversity | SOI       | RTD/                     | CNT                | Rotaxane         | GMR/               | Quantum dot          |

|             | Si-Ge     | HFET                     | C60 logic          | molecular        | CMR                | Quantum              |

|             | Dual-gate | RTT                      | & memory           | x-bar            | MQCA               | diffraction          |

|             | Vertical  | logic &<br>memory        | Nanotube           | CAEN             | Hybrid-            | FET                  |

|             | FET       | Multi-                   | array logic        | Coulomb-         | Hall effect        | Quantum interference |

|             | Ballistic | valued                   | Large-             | coupled          | Molecular          | devices              |

|             | nano-FET  | logic                    | bandgap<br>devices | optically pumped | nano-<br>magnetics | surface super-       |

|             |           | nano-<br>pipelining      | (AlN, BN)          | nanodevices      | Magnetic           | lattices             |

|             |           |                          |                    | DNA              | RTD                | RSFQ                 |

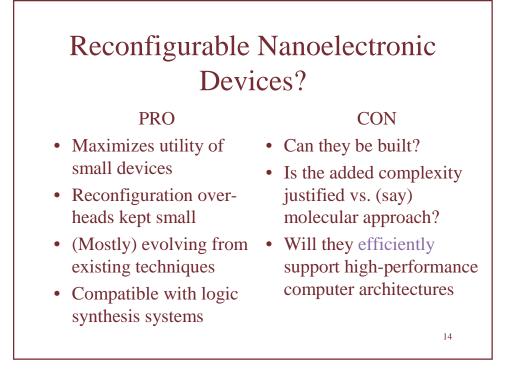

#### The "Ideal" Nanocomputer Platform? Very large, scalable with rich, local connectivity Built from simple devices that exhibit: • **High functionality (?)** \_ Gain > 1\_ Static (at least) and preferably non-volatile operation (Very) low power density \_ **Room temperature operation** \_ Reliable and fault tolerant Preferably no intrinsic reliance on any form of • global signal (e.g. a master clock) Reconfigurable in operation, with little or no • performance penalty 4

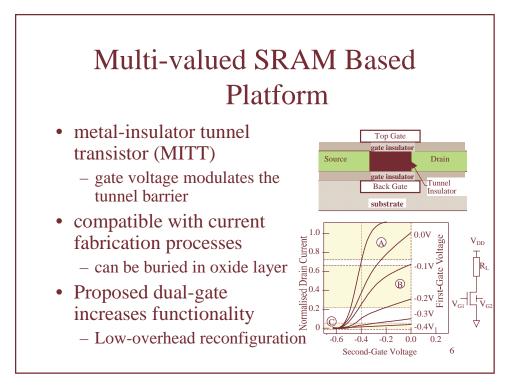

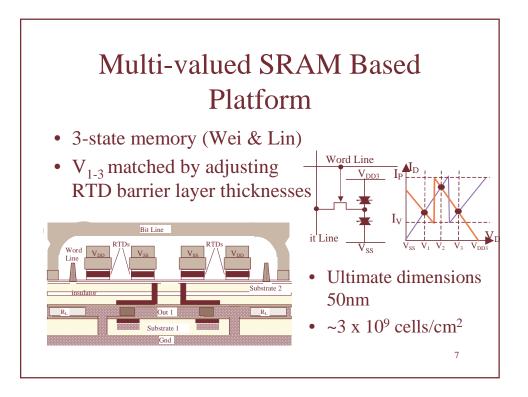

- 1. Multi-valued SRAM Based Platform

- RTD multi-valued RAM

- Dual-gate transistors

- 2. Phase Transition Device Based Platform

5

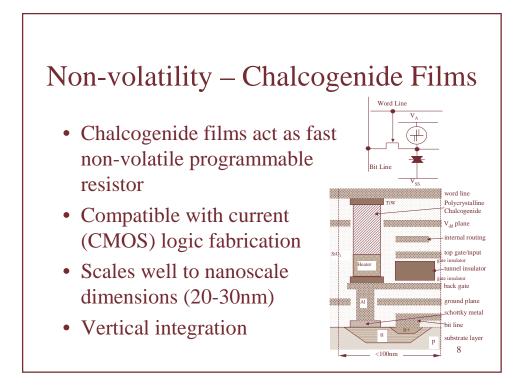

- Resistive thin-films

- 3. A Nano-Magnetic Platform

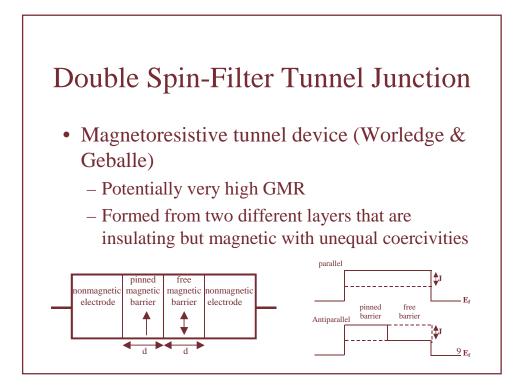

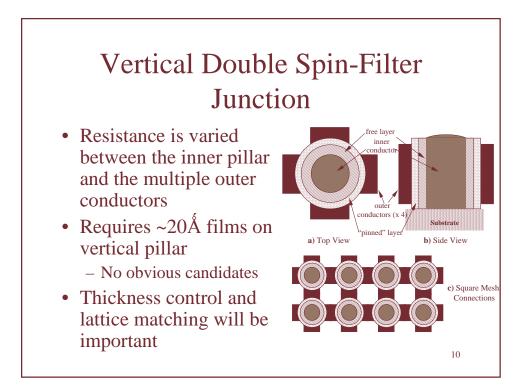

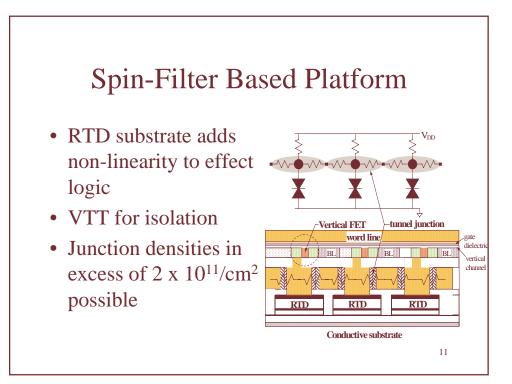

- Double spin-filter junction

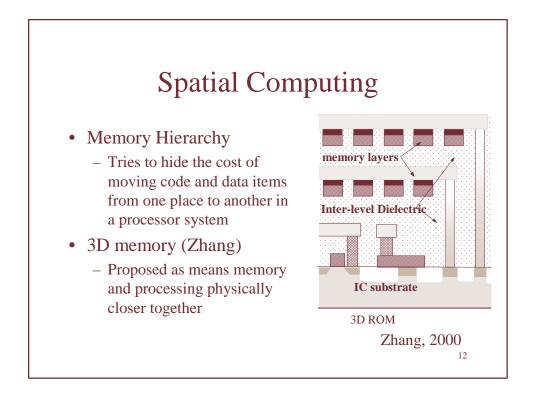

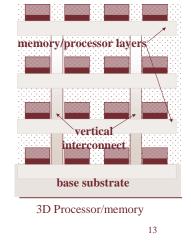

## A 3D Reconfigurable Computing Platform

- Merged processor/ memory into 3D structure

- Reduced memory performance gap

- Extreme memory bandwidth

- Processing-in-memory; processing-is-memory

### What's Next?

- Simulation of nano-magnetic materials

- Characterization of typical junctions

e.g. tunneling conductance

- Simulation of GMR-based array platform

15

• Development of Spatial Computing techniques suited to this platform

And in the long term? • "Decimation followed by diversification" (Gould) • Test against the "environment" – ease of fabrication, cost, ease of use etc. • Extinction for some, consolidation and growth for others

# Towards a Reconfigurable Nanocomputer Platform

## Thank You

Paul Beckett