## **Exam details**

- **Closed book, closed notes**

- A4 paper

- Covers all lecture material through Lecture on Snooping-Based **Multiprocessor Design**

- Must use either blue or black pen (no pencils or other pen colors)

- Typical question formats:

- Short answer

- Multiple choice with explanations

## sin(x) in ISPC

### "Interleaved" assignment of array elements to program instances

C++ code: main.cpp

```

#include "sinx_ispc.h"

int N = 1024;

int terms = 5;

float* x = new float[N];

float* result = new float[N];

// initialize x here

```

```

// execute ISPC code

sinx(N, terms, x, result);

```

### **ISPC Keywords:**

programCount: number of simultaneously

executing instances in the gang (uniform value)

programIndex: id of the current instance in the

gang. (a non-uniform value: "varying")

uniform: A type modifier. All instances have the same value for this variable. Its use is purely an optimization. Not needed for correctness.

```

export void sinx(

uniform int N,

uniform int terms,

uniform float* x,

uniform float* result)

{

// assumes N % programCount = 0

for (uniform int i=0; i<N; i+=programCount)</pre>

{

int idx = i + programIndex;

float value = x[idx];

float numer = x[idx] * x[idx] * x[idx];

uniform int denom = 6; // 3!

uniform int sign = -1;

for (uniform int j=1; j<=terms; j++)</pre>

value += sign * numer / denom

numer *= x[idx] * x[idx];

denom *= (2*j+2) * (2*j+3);

sign *= -1;

result[idx] = value;

}

```

### ISPC code: sinx.ispc

## sin(x) in ISPC: version 2 "Blocked" assignment of elements to instances

**C++ code:** main.cpp

```

#include "sinx_ispc.h"

int N = 1024;

int terms = 5;

float* x = new float[N];

float* result = new float[N];

// initialize x here

```

// execute ISPC code sinx(N, terms, x, result); export void sinx( uniform int N, ł

### **ISPC code:** sinx.ispc

```

uniform int terms,

uniform float* x,

uniform float* result)

// assume N % programCount = 0

uniform int count = N / programCount;

int start = programIndex * count;

for (uniform int i=0; i<count; i++)</pre>

int idx = start + i;

float value = x[idx];

float numer = x[idx] * x[idx] * x[idx];

uniform int denom = 6; // 3!

uniform int sign = -1;

for (uniform int j=1; j<=terms; j++)</pre>

value += sign * numer / denom

numer *= x[idx] * x[idx];

denom *= (j+3) * (j+4);

sign *= -1:

result[idx] = value;

```

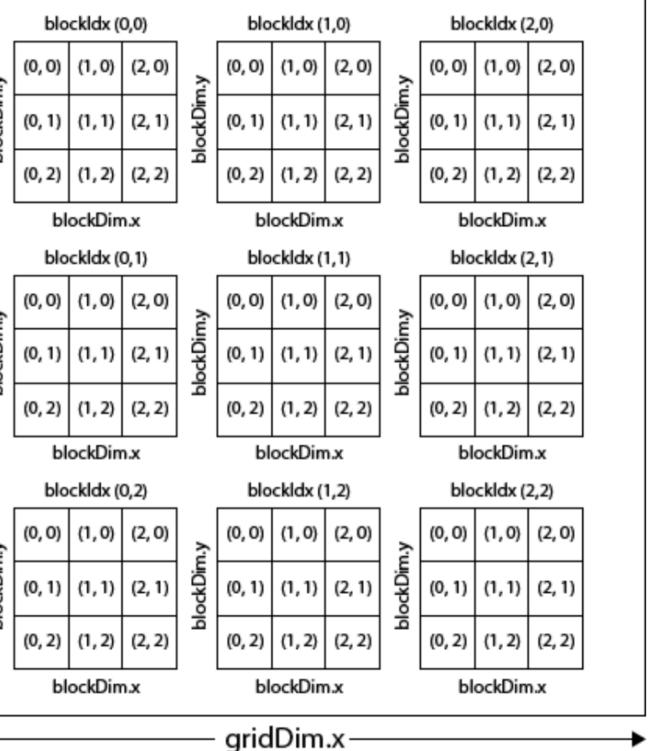

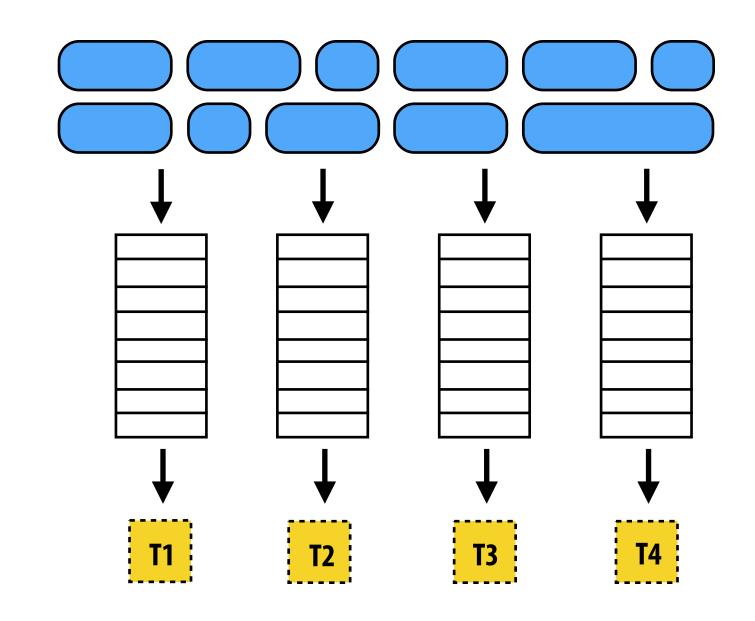

# Grid, Block, and Thread

- gridDim: The dimensions of the grid

- blockIdx: The block index within the grid

- blockDim: The dimensions of the block

- threadIdx: The thread index within the block

Why not have gridldx and threadDim?

| Î            |   |            |

|--------------|---|------------|

|              |   | blockDim.y |

| - gridDim .y |   | blockDim.y |

|              |   | blockDim.y |

| •            | • |            |

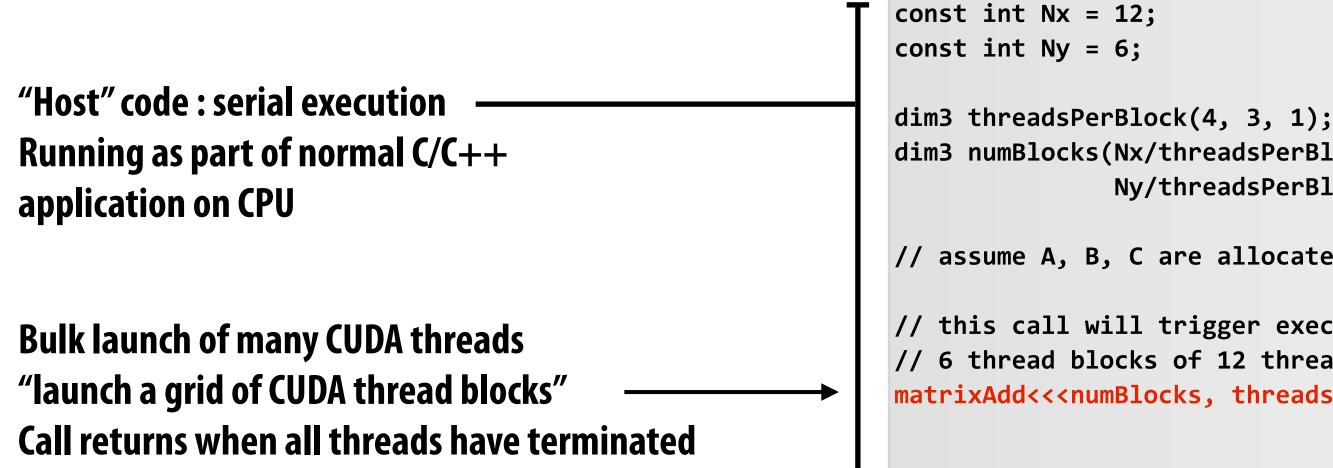

# **Basic CUDA syntax**

### **Regular application thread running on CPU (the "host")**

### SPMD execution of device kernel function:

```

dim3 numBlocks(Nx/threadsPerBlock.x,

Ny/threadsPerBlock.y, 1);

// assume A, B, C are allocated Nx x Ny float arrays

// this call will trigger execution of 72 CUDA threads:

// 6 thread blocks of 12 threads each

matrixAdd<<<numBlocks, threadsPerBlock>>>(A, B, C);

```

### **CUDA kernel definition**

```

global___ void matrixAdd(float A[Ny][Nx],

float B[Ny][Nx],

float C[Ny][Nx])

int i = blockIdx.x * blockDim.x + threadIdx.x;

int j = blockIdx.y * blockDim.y + threadIdx.y;

C[j][i] = A[j][i] + B[j][i];

```

# **CUDA** synchronization constructs

### syncthreads()

Barrier: wait for all threads in the block to arrive at this point

### Atomic operations

- e.g., float atomicAdd(float\* addr, float amount)

- Atomic operations on both global memory and shared memory variables

### Host/device synchronization

Implicit barrier across all threads at return of kernel

## Shared address space solver (SPMD execution model)

```

int

// grid size

n;

done = false;

bool

diff = 0.0;

float

LOCK

myLock;

BARRIER myBarrier;

// allocate grid

float* A = allocate(n+2, n+2);

void solve(float* A) {

iteration.

float myDiff;

int threadId = getThreadId();

int myMin = 1 + (threadId * n / NUM_PROCESSORS);

int myMax = myMin + (n / NUM_PROCESSORS)

while (!done) {

float myDiff = 0.f;

diff = 0.f;

barrier(myBarrier, NUM_PROCESSORS);

for (j=myMin to myMax) {

for (i = red cells in this row) {

float prev = A[i,j];

A[i,j] = 0.2f * (A[i-1,j] + A[i,j-1] + A[i,j] +

A[i+1,j], A[i,j+1]);

myDiff += abs(A[i,j] - prev));

lock(myLock);

diff += myDiff;

unlock(myLock);

barrier(myBarrier, NUM_PROCESSORS);

if (diff/(n*n) < TOLERANCE)</pre>

done = true;

barrier(myBarrier, NUM PROCESSORS);

}

```

Grid solver example from: Culler, Singh, and Gupta

### Improve performance by accumulating into partial sum locally, then complete reduction globally at the end of the

compute per worker partial sum

Now only lock once per thread, not once per (i,j) loop iteration!

// check convergence, all threads get same answer

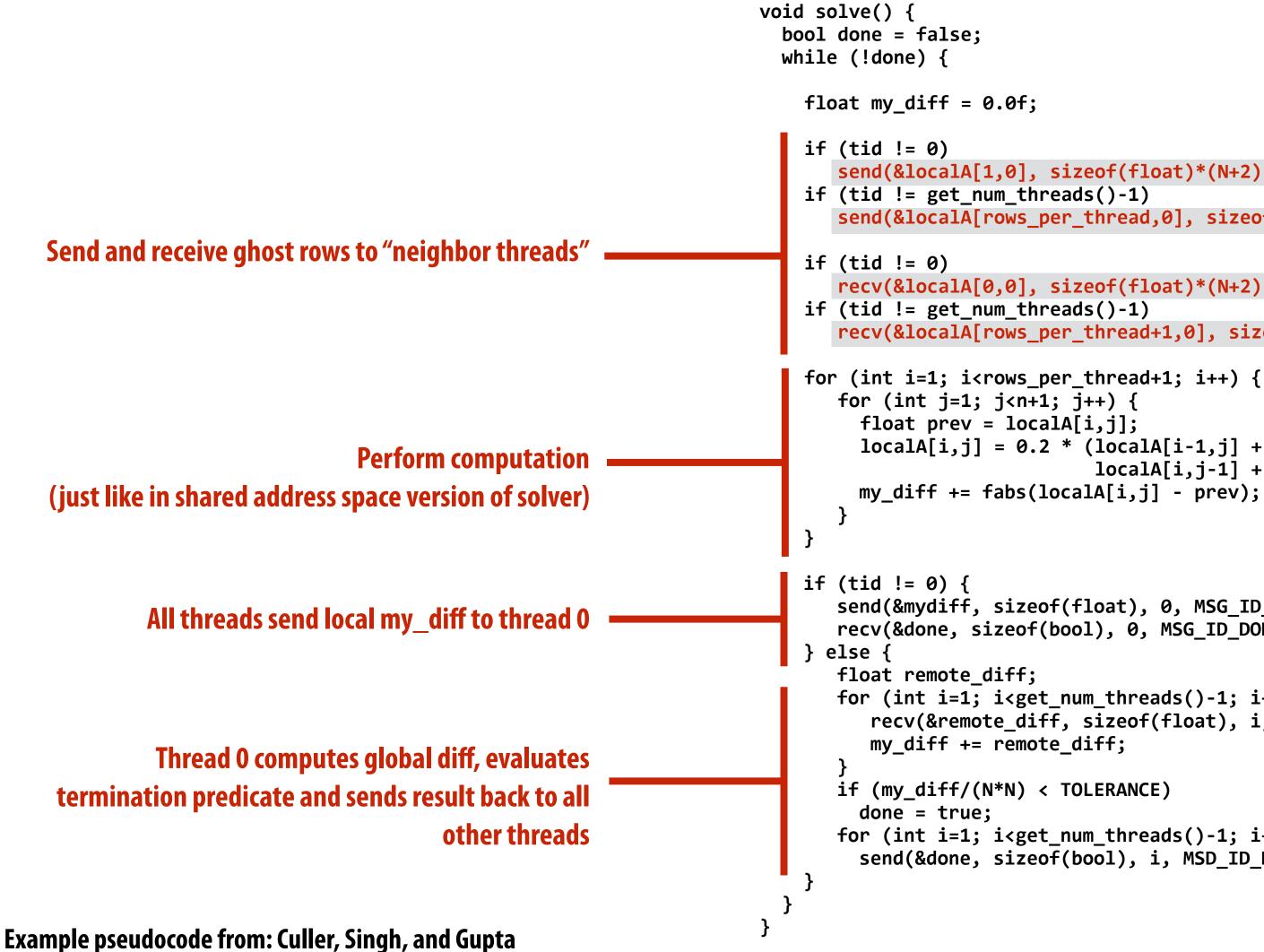

### Message passing solver int N; int tid = get\_thread\_id(); int rows per thread = N / A

Similar structure to shared address space solver, but now communication is explicit in message sends and receives

```

int rows_per_thread = N / get_num_threads();

float* localA = allocate(rows_per_thread+2, N+2);

// assume localA is initialized with starting values

// assume MSG_ID_ROW, MSG_ID_DONE, MSG_ID_DIFF are constants used as msg ids

send(&localA[1,0], sizeof(float)*(N+2), tid-1, MSG_ID_ROW);

send(&localA[rows_per_thread,0], sizeof(float)*(N+2), tid+1, MSG_ID_ROW);

recv(&localA[0,0], sizeof(float)*(N+2), tid-1, MSG_ID_ROW);

recv(&localA[rows_per_thread+1,0], sizeof(float)*(N+2), tid+1, MSG_ID_ROW);

localA[i,j] = 0.2 * (localA[i-1,j] + localA[i,j] + localA[i+1,j] +

localA[i,j-1] + localA[i,j+1]);

send(&mydiff, sizeof(float), 0, MSG ID DIFF);

recv(&done, sizeof(bool), 0, MSG_ID_DONE);

for (int i=1; i<get_num_threads()-1; i++) {</pre>

recv(&remote_diff, sizeof(float), i, MSG_ID_DIFF);

for (int i=1; i<get_num_threads()-1; i++)</pre>

send(&done, sizeof(bool), i, MSD_ID_DONE);

```

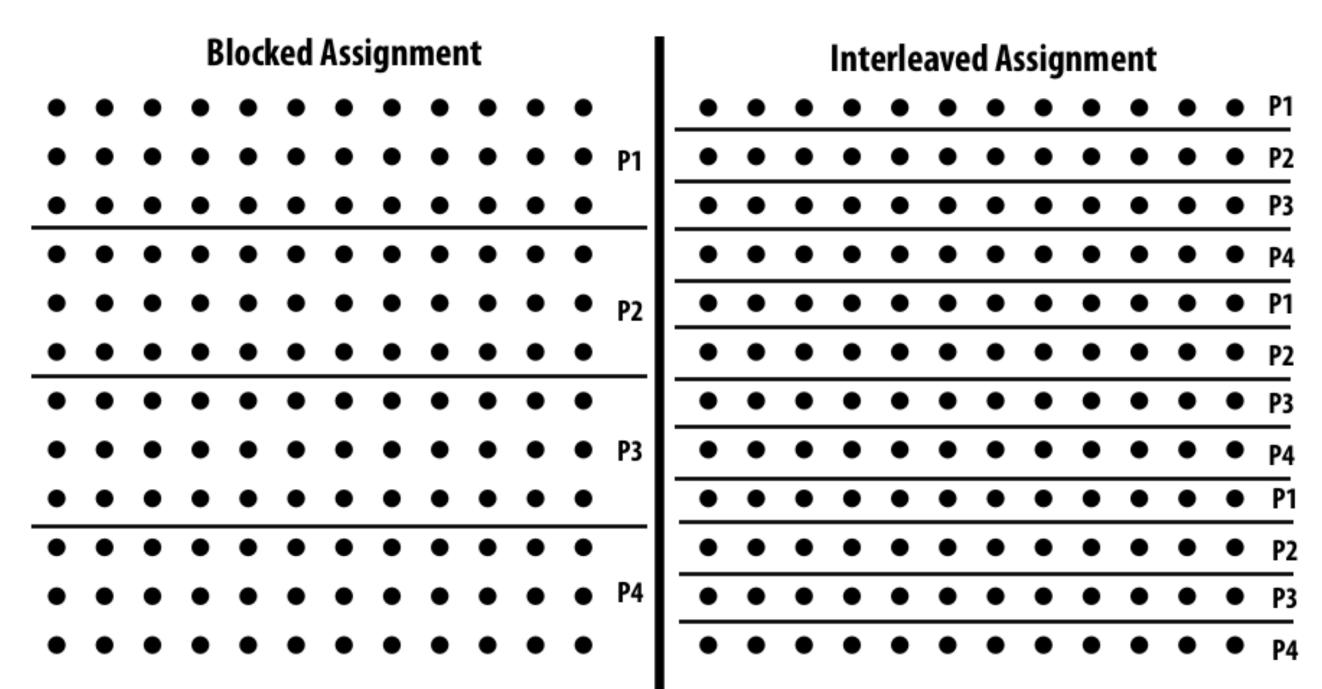

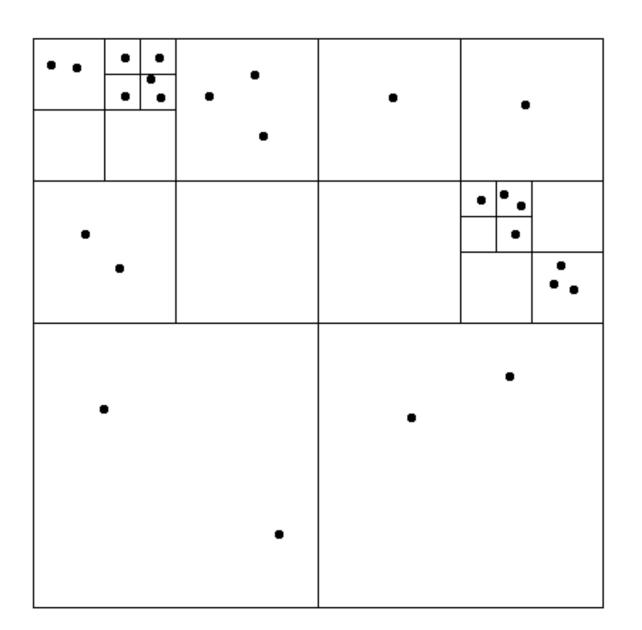

# Static assignment

- Assignment of work to threads is pre-determined

- Not necessarily determined at compile-time (assignment algorithm may depend on runtime parameters such as input data size, number of threads, etc.)

- **Recall solver example: assign equal number of grid cells (work) to each thread (worker)**

- We discussed two static assignments of work to workers (blocked and interleaved)

Good properties of static assignment: simple, essentially zero runtime overhead (in this example: extra work to implement assignment is a little bit of indexing math)

# "Semi-static" assignment

- Cost of work is predictable for near-term future

- Idea: recent past good predictor of near future

- Application periodically profiles itself and re-adjusts assignment

- Assignment is "static" for the interval between re-adjustments

**Particle simulation:**

**Redistribute particles as they move** over course of simulation (if motion is slow, redistribution need not occur often)

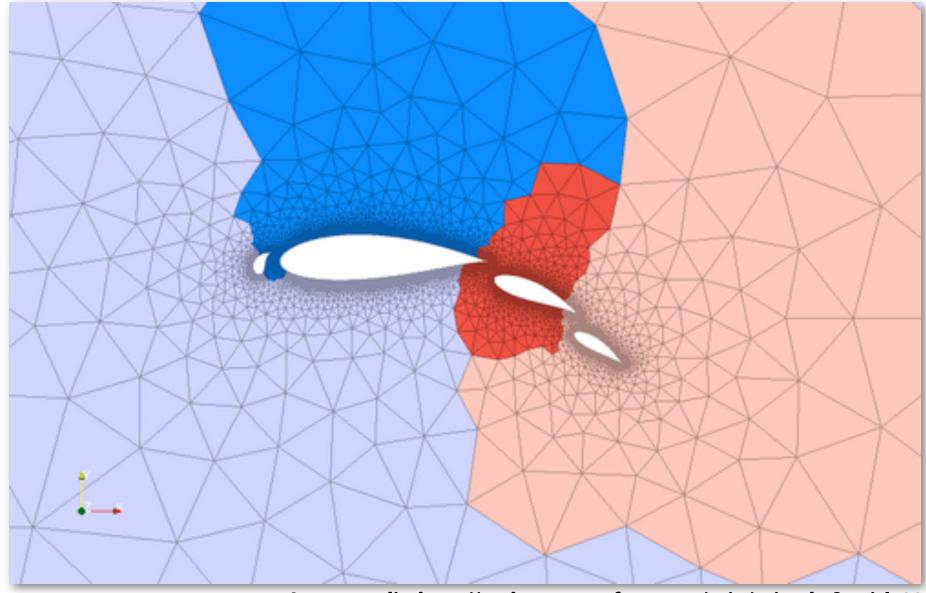

Adaptive mesh:

Mesh is changed as object moves or flow over object changes, but changes occur slowly (color indicates assignment of parts of mesh to processors)

Image credit: http://typhon.sourceforge.net/spip/spip.php?article22

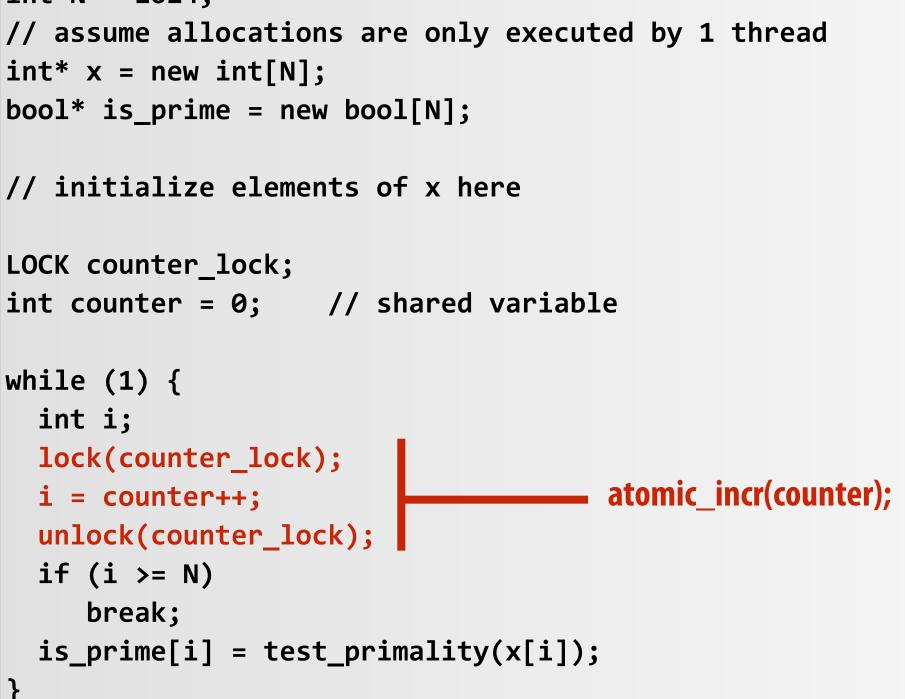

# **Dynamic assignment**

### Program determines assignment dynamically at runtime to ensure a well distributed load. (The execution time of tasks, or the total number of tasks, is unpredictable.)

Sequential program (independent loop iterations)

```

int N = 1024;

int* x = new int[N];

bool* prime = new bool[N];

// initialize elements of x here

for (int i=0; i<N; i++)</pre>

{

// unknown execution time

is_prime[i] = test_primality(x[i]);

}

```

```

int N = 1024;

int* x = new int[N];

bool* is prime = new bool[N];

// initialize elements of x here

LOCK counter_lock;

int counter = 0; // shared variable

while (1) {

int i;

lock(counter_lock);

i = counter++;

unlock(counter_lock);

if (i \ge N)

break;

is prime[i] = test_primality(x[i]);

```

### Parallel program (SPMD execution by multiple threads, shared address space model)

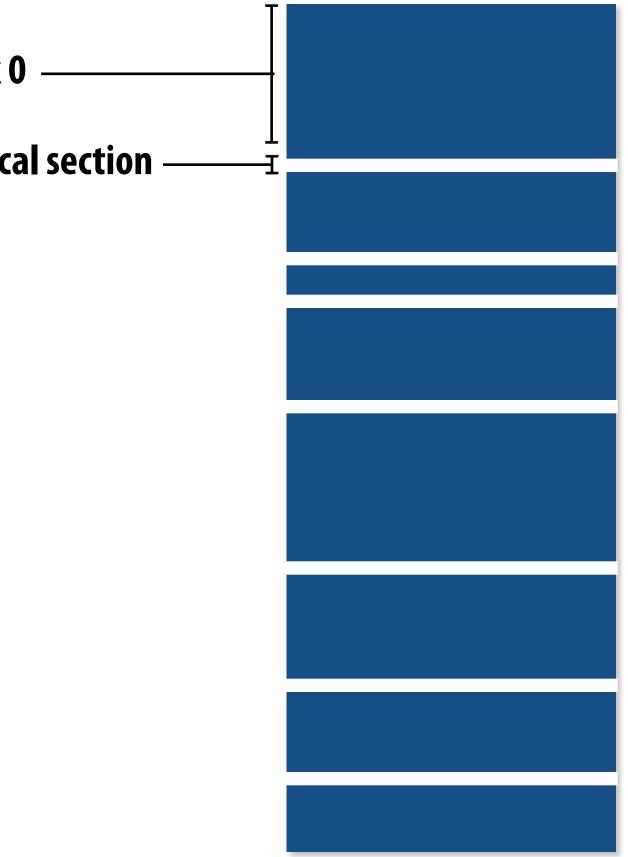

# Increasing task granularity

```

const int N = 1024;

const int GRANULARITY = 10;

// assume allocations are only executed by 1 thread

float* x = new float[N];

bool* prime = new bool[N];

// initialize elements of x here

LOCK counter_lock;

int counter = 0;

while (1) {

int i;

lock(counter_lock);

i = counter;

counter += GRANULARITY;

unlock(counter_lock);

if (i \ge N)

break;

int end = min(i + GRANULARITY, N);

for (int j=i; j<end; j++)</pre>

is_prime[j] = test_primality(x[j]);

```

**Coarse granularity** partitioning: 1 "task" = 10 elements **Decreased synchronization cost** (Critical section entered 10 times less)

Time in task 0

Time in critical section

# **Distributed work queues**

### **Costly synchronization/communication occurs during stealing**

- But not every time a thread takes on new work

- **Stealing occurs only when necessary to ensure good load balance**

- Leads to increased locality

- **Common case: threads work on tasks they create (producer-consumer locality)**

- Implementation challenges

- Who to steal from?

- How much to steal?

- How to detect program termination?

- **Ensuring local queue access is fast** (while preserving mutual exclusion)

# **Cache coherence**

## Why cache coherence?

Hand-wavy answer: would like shared memory to behave "intuitively" when two processors read and write to a shared variable. Reading a value after another processor writes to it should return the new value. (despite replication due to caches)

## **Requirements of a coherent address space**

- A read by processor P to address X that follows a write by P to address X, should return the value of the write by P (assuming no other processor wrote to X in between)

- A read by a processor to address X that follows a write by another processor to X returns the written value... 2. if the read and write are sufficiently separated in time (assuming no other write to X occurs in between)

- 3. Writes to the same location are serialized; two writes to the same location by any two processors are seen in the same order by all processors. (Example: if values 1 and then 2 are written to address X, no processor observes 2 before 1)

Condition 1: program order (as expected of a uniprocessor system)

**Condition 2:** write propagation: The news of the write has to eventually get to the other processors. Note that precisely when it is propagated is not defined by definition of coherence.

**Condition 3: write serialization**

## Implementing cache coherence

Main idea of invalidation-based protocols: before writing to a cache line, obtain exclusive access to it

**SNOOPING**

Each cache broadcasts its cache misses to all other caches. Waits for other caches to react before continuing. **Good:** simple, low latency **Bad: broadcast traffic limits scalability**

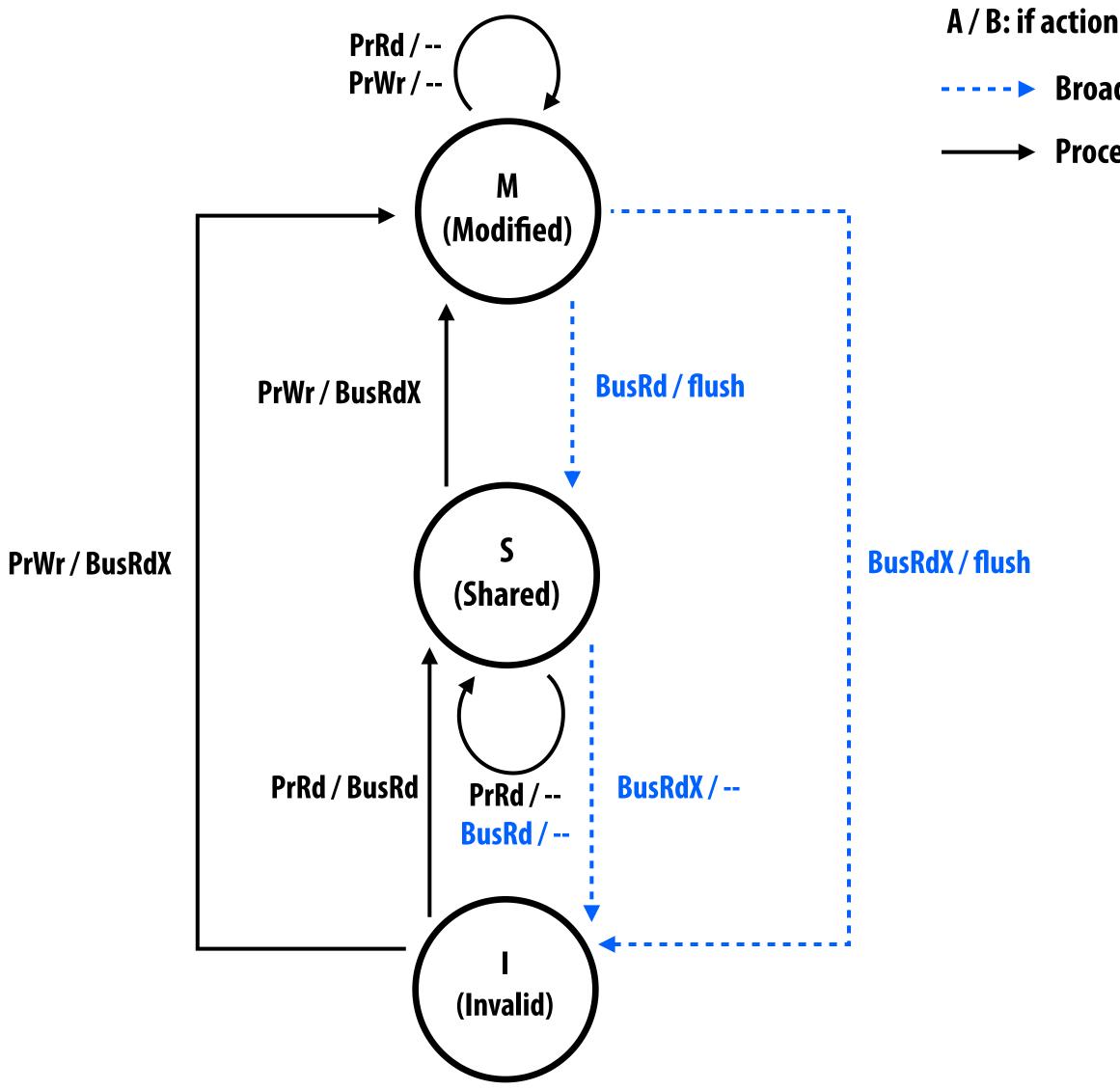

## MSI state transition diagram

A / B: if action A is observed by cache controller, action B is taken

Broadcast (bus) initiated transaction

→ Processor initiated transaction

# Assignment 2, Problem 3

| Action                     | <b>P0 X</b> | <b>P0 Y</b> | P1 X | P1 Y |

|----------------------------|-------------|-------------|------|------|

| Initial                    |             | I           | l    | I    |

| PO: LD X                   | S/0         |             |      |      |

| P1: LD X                   | S/0         |             | S/0  |      |

| <b>P0: ST X</b> ← 1        | <b>M/1</b>  |             |      |      |

| <b>P0: ST X</b> ← <b>2</b> | M/2         |             |      |      |

| P1: ST X ← 3               | I           |             | M/3  |      |

| P1: LD X                   |             |             | M/3  |      |

| PO: LD X                   | S/3         |             | S/3  |      |

| <b>P0: ST X</b> ← 4        | M/4         |             | I    |      |

| P1: LD X                   | S/4         |             | S/4  |      |

| PO: LD Y                   |             | S/0         |      |      |

| <b>P0: ST Y</b> ← 1        | S/4         | M/1         | S/4  |      |

| P1: ST Y ← 2               |             |             |      | M/2  |

X and Y have value 0 at start of execution.

# Inclusion property of caches

All lines in closer [to processor] cache are also in farther [from processor] cache

- e.g., contents of L1 are a subset of contents of L2

- Thus, all transactions relevant to L1 are also relevant to L2, so it is sufficient for only the L2 to snoop the interconnect

If line is in owned state (M in MSI/MESI) in L1, it must also be in owned state in L2

- Allows L2 to determine if a bus transaction is requesting a modified cache line in L1 without requiring information from L1

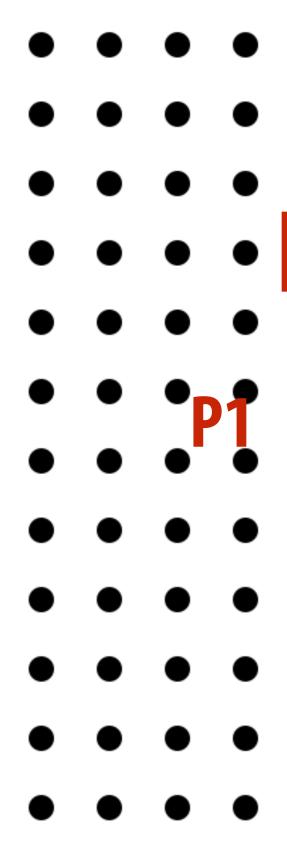

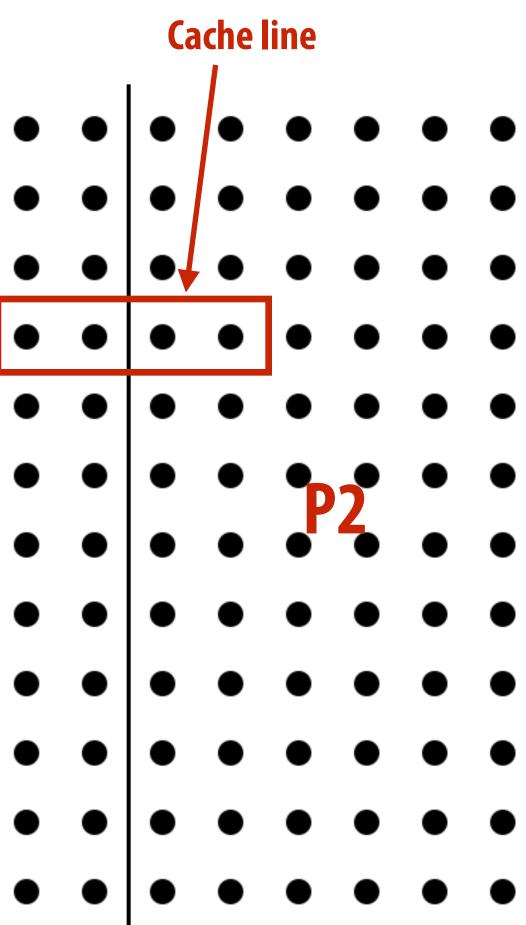

# Artifactual vs. inherent communication

## INHERENT COMMUNICATION

## ARTIFACTUAL COMMUNICATION

### FALSE SHARING

Problem assignment as shown. Each processor reads/writes only from its local data.

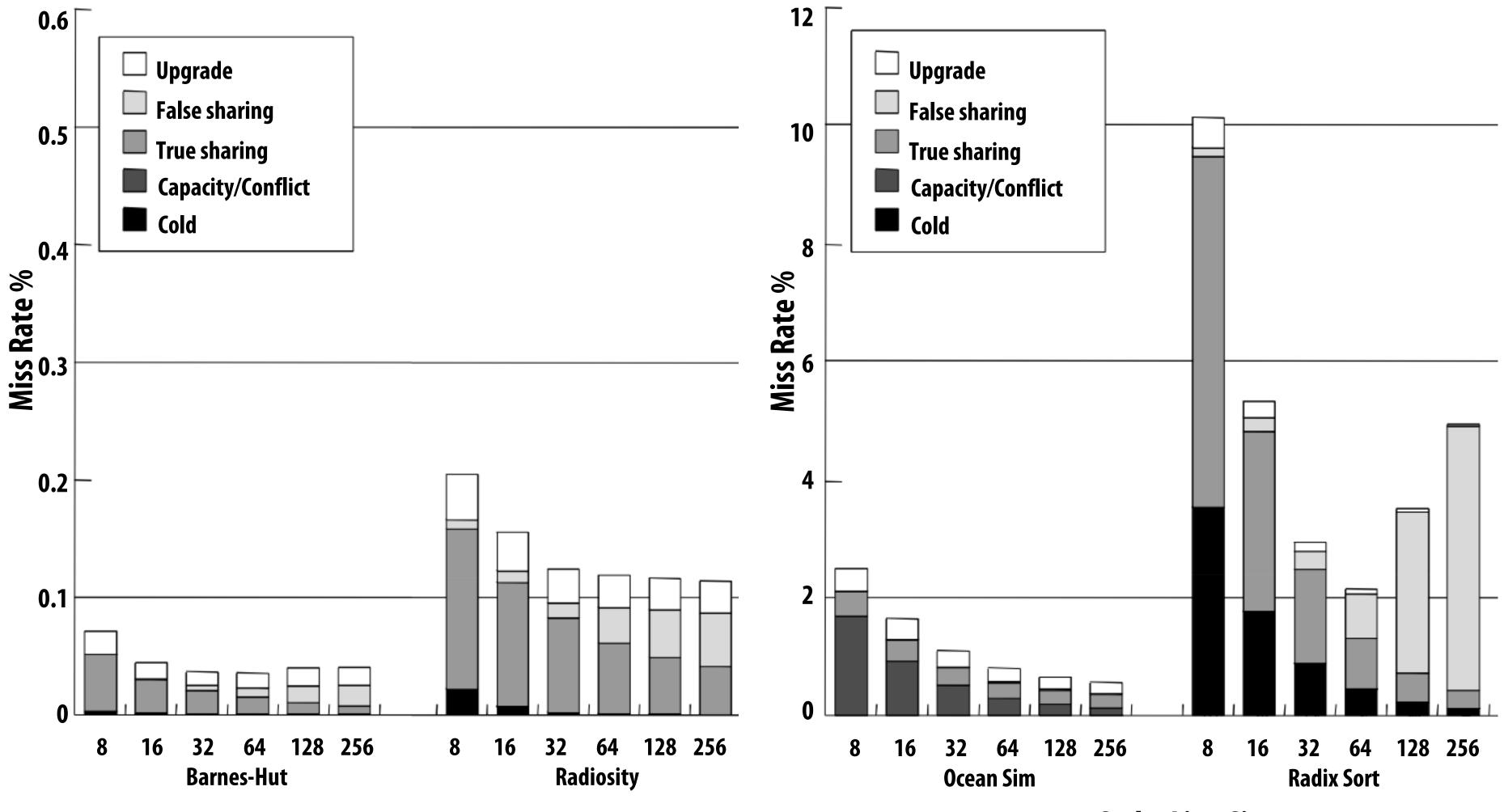

### **Impact of cache line size on miss rate** Results from simulation of a 1 MB cache (four example applications)

\* Note: I separated the results into two graphs because of different Y-axis scales Figure credit: Culler, Singh, and Gupta

**Cache Line Size**

**Cache Line Size**

## Implementing cache coherence

## Main idea of invalidation-based protocols: before writing to a cache line, obtain exclusive access to it

## **SNOOPING**

Each cache broadcasts its cache misses to all other caches. Waits for other caches to react before continuing. **Good:** simple, low latency **Bad: broadcast traffic limits scalability**

## DIRECTORIES

Information about location of cache line and number of shares is stored in a centralized location. On a miss, requesting cache queries the directory to find sharers and communicates with these nodes using <u>point-to-point</u> messages. Different implementation of directories. Good: coherence traffic scales with number of sharers, and number of sharers is usually low **Bad: higher complexity, overhead of directory storage, additional latency** due to longer critical path

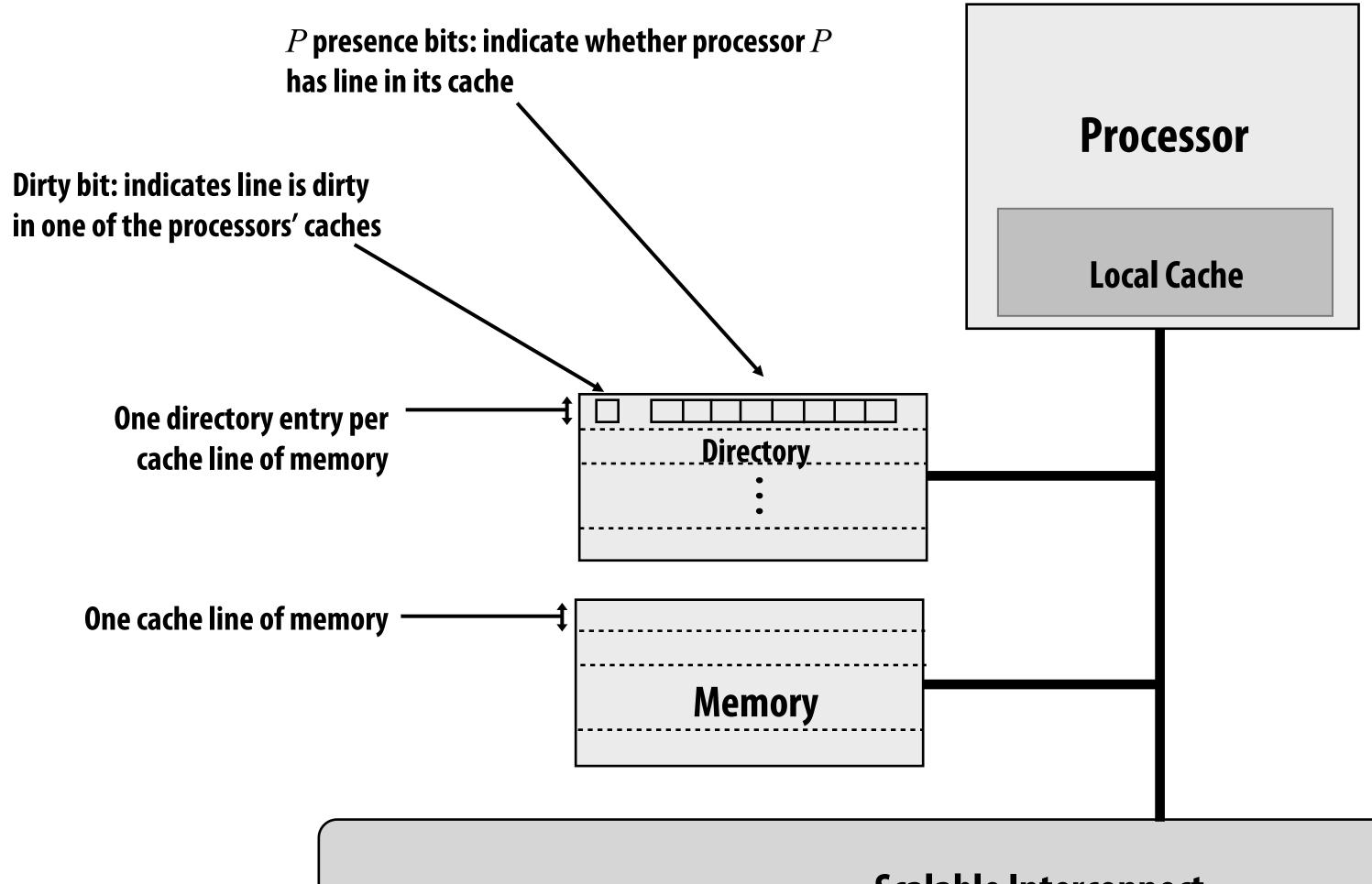

# A very simple directory

### Scalable Interconnect

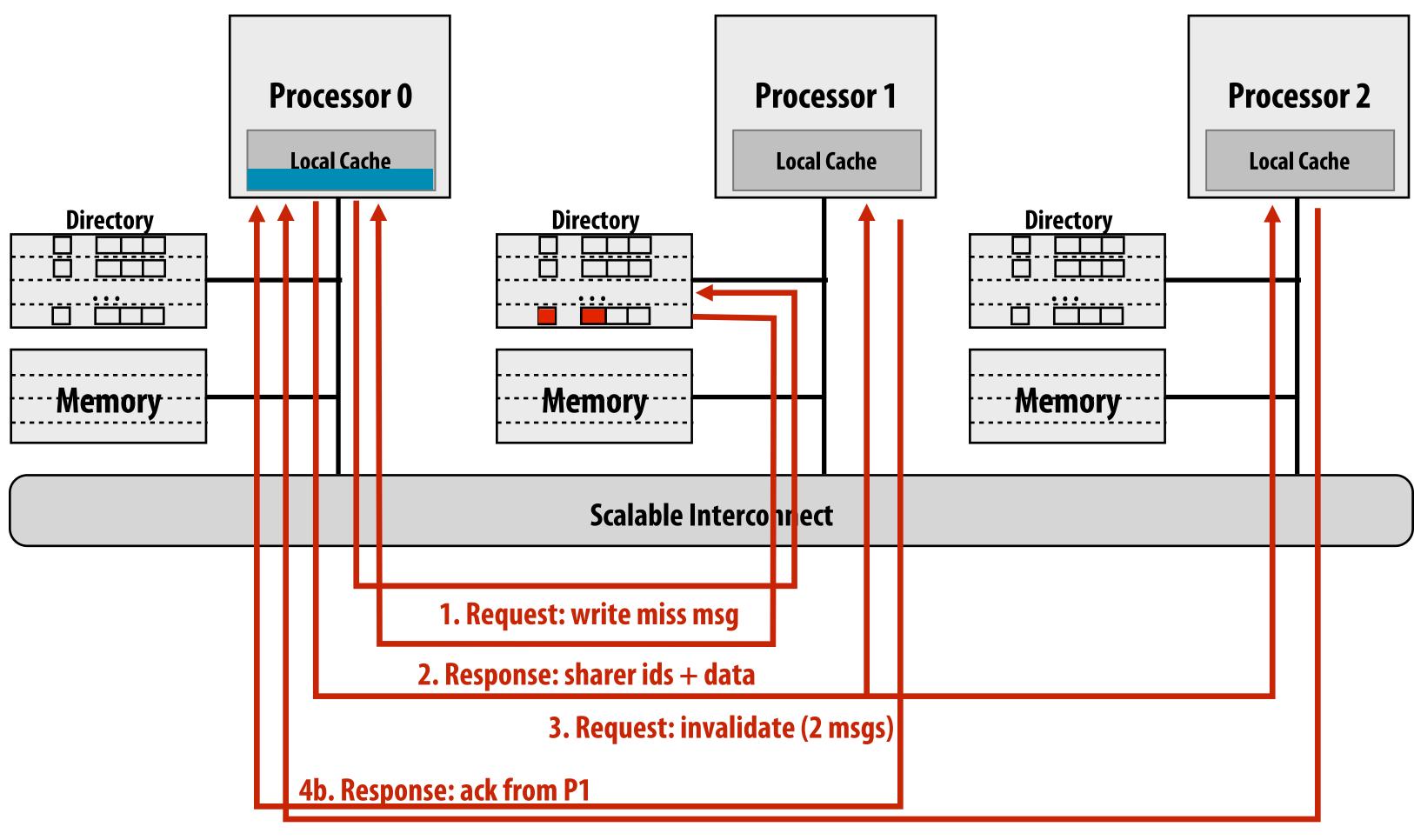

# **Example 3: write miss**

Write to memory by processor 0: line is clean, but resident in P1's and P2's caches

<sup>4</sup>a. Response: ack from P2

After receiving both invalidation acks, P0 can perform write

# **Reducing storage overhead of directory**

### **Optimizations on full-bit vector scheme**

- **Increase cache line size (reduce M term)**

- What are possible problems with this approach? (consider graphs from last lecture)

- Group multiple processors into a single directory "node" (reduce P term)

- Need only one directory bit per node, not one bit per processor

- Hierarchical: could use snooping protocol to maintain coherence among processors in a node, directory across nodes

### We will now discuss two alternative schemes

- Limited pointer schemes (reduce P)

- **Sparse directories**