## MVCS-TM: Multiversion Conflict Serializable Hardware Transactional Memory

## **Overview**

Problem:

- Commercial implementations of Hardware Transactional Memory are overly restrictive. Only small transactions can be supported

- Conflict resolution mechanism using cache coherence is sufficient, but only low degrees of parallelism is achieved

## Solution:

- HTM systems must overflow transactional states into DRAM to support large transactions

- Instead of relying on 2PL-style cache coherence for conflict detection, we leverage Optimistic Concurrency Control for better parallelism

## **Motivation**

Stanford SI-TM (Snapshot-Isolation TM):

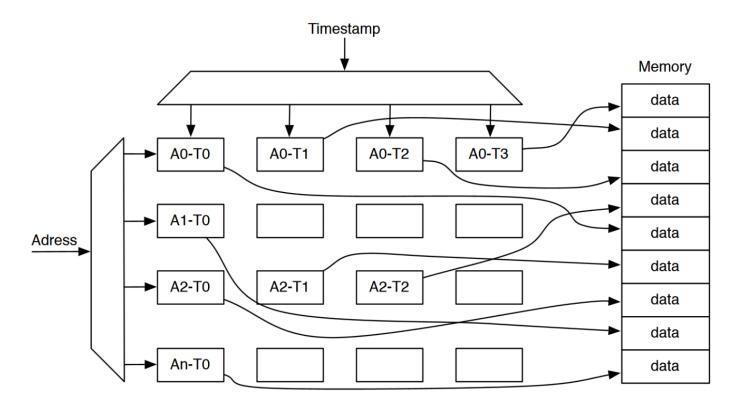

- Physical address space is multiversioned

- A special hardware device, the Multiversion Manager (MVM), is inserted between the L2 and shared LLC

- Transactional instructions access memory with a timestamp. Given a physical address and a timestamp, the MVM translates them into the physical address to the versioned storage

- At most four versions are supported

**Figure 1. The Multiversion Manager (MVM)**

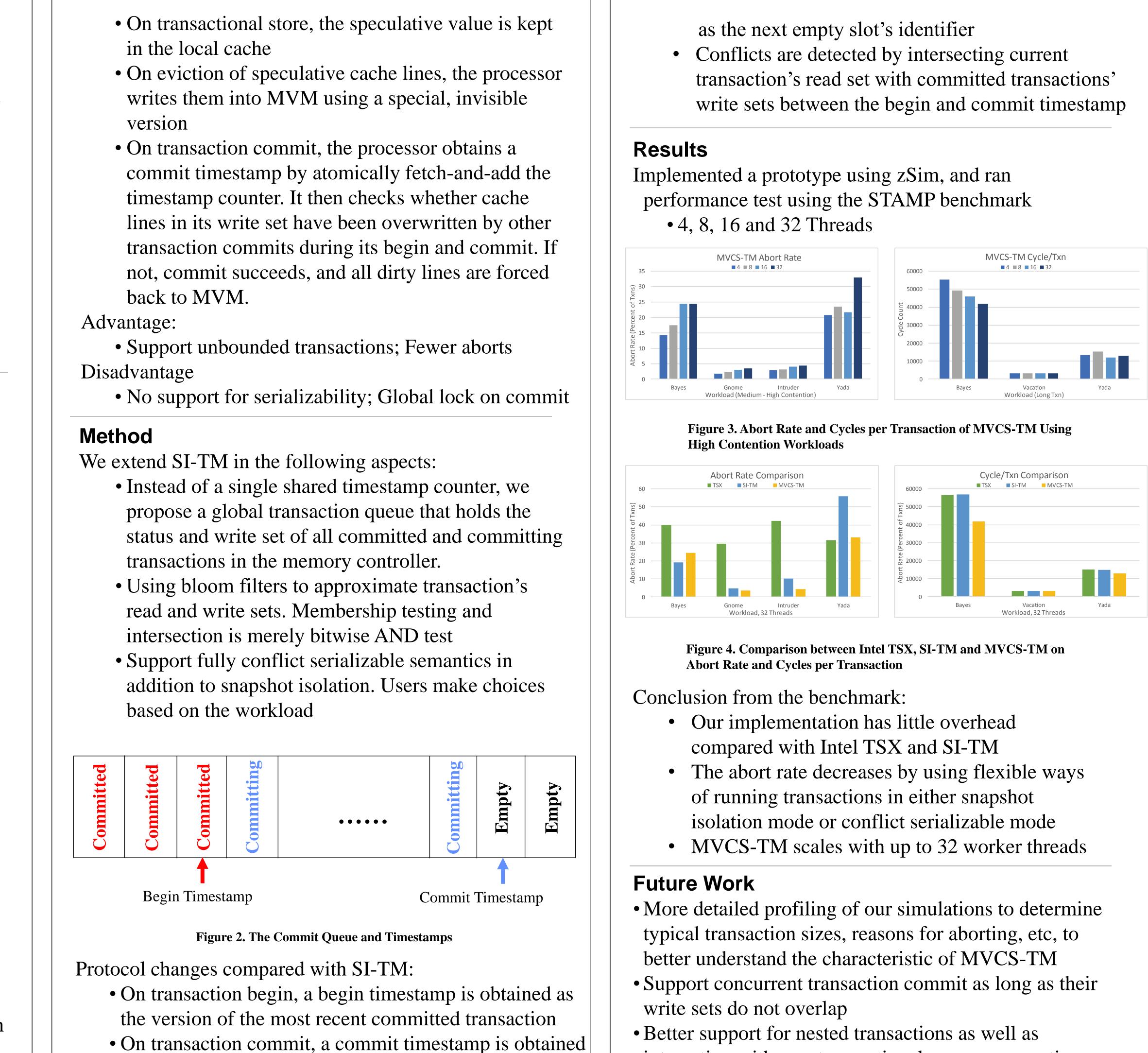

SI-TM transaction commit and begin protocol:

- A global shared timestamp counter provides monotonically increasing source of timestamps

- On transaction begin, the counter is read as the begin timestamp of the transaction

- On transactional load, the processor uses the begin timestamp as the version to access MVM

Ziqi Wang, Hao Wei Computer Science Department Carnegie Mellon University

- interaction with non-transactional memory operations